03/06/2013 Giovanni Salvador

DC10581

# **AN00152: Interfacing FlashRunner** with Texas Instruments CC253x **Devices**

FlashRunner is a Universal In-System Programmer, which uses the principles of In-Circuit Programming to program Texas Instruments CC253x family microcontrollers. This Application Note describes how to properly set up and use FlashRunner to program CC253x Flash devices.

This Application Note assumes that you are familiar with both FlashRunner and the main features of the CC253x family. Full documentation about these topics is available in the FlashRunner user's manual and in device-specific datasheets.

#### 1. Introduction

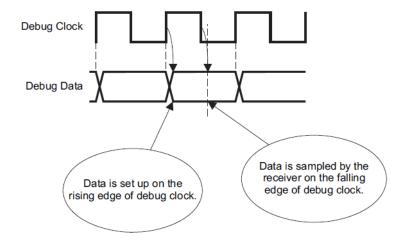

In-system programming of CC253x microcontrollers is performed through the debug interface. The debug interface uses a SPI like two-wire interface consisting of a debug data and debug clock signals. Data is driven on the bi-directional debug-data pin at the positive edge of the debug clock and data is sampled on the falling edge of this clock.

In order to use FlashRunner to perform in-system programming, you need to implement the appropriate in-circuit programming hardware interface on your application board.

Thanks to its in-system programming capabilities, FlashRunner allows you to program or update the content of the Flash memory when the chip is already plugged on the application board.

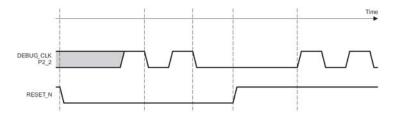

During the entry phase the algorithm force two falling-edge transitions on pin P2.2, that is the debug clock, while the RESET\_N input is held low:

When the RESET\_N line is set high, the device is in debug mode.

## 2. Hardware Configuration

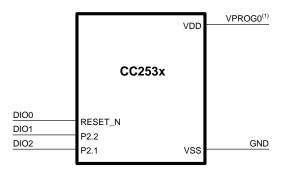

The microcontroller's lines needed to program a CC253x device are the following:

RESET\_N: Reset, active low.

P2.1: Debug data.

P2.2: Debug clock.

The lines mentioned above must be connected to the FlashRunner's "ISP" connector according to the following diagram:

(1) Connect this line if you want FlashRunner to automatically power the target device

## 3. Specific TCSETPAR Programming Commands

#### Overview

TCSETPAR commands set device-specific and programming algorithm-specific parameters. These commands must be sent after the TCSETDEV command and before a TPSTART / TPEND command block.

All of the following parameters must be correctly specified through the relative TCSETPAR commands (although the order with which these parameters are set is not important):

- VDD voltage;

- Power Up time;

- Power Down time:

- Reset Up time;

- Reset Down time;

- SCLK communication frequency.

#### **TPSETPAR VDD**

Command syntax:

TCSETPAR VDD <voltage mV>

Parameters:

voltage mv: Target device supply voltage, expressed in millivolts.

#### Description:

This command is used to properly generate the voltage level of the RESET\_N, Debug Clock and Debug Data signals. Additionally, the specified voltage is routed to the VPROG0 line of the FlashRunner's "ISP" connector, which can be used as a supply voltage for the target board.

#### **TPSETPAR PWUP**

Command syntax:

TCSETPAR PWUP <time ms>

Parameters:

time ms: Power rising time, expressed in milliseconds.

#### Description:

This command is necessary because, to enter the programming mode, FlashRunner must properly drive the  $V_{DD}$  line during the power-on reset.

The V<sub>DD</sub> rising time (PWUP) is expressed in milliseconds and depends on the features of your target board. Make sure to choose a value large enough to ensure that the  $V_{\scriptscriptstyle DD}$ signal reaches the high logic level within the specified time. Note that, if the V<sub>DD</sub> line has a high load, a longer time is required for the  $V_{\scriptscriptstyle DD}$  signal to reach the high logic level. If PWUP is not long enough, FlashRunner could not be able to enter the programming mode.

#### **TPSETPAR PWDOWN**

Command syntax:

TCSETPAR PWDOWN <time ms>

Parameters:

time ms: Power falling time, expressed in milliseconds.

Description:

The V<sub>DD</sub> falling time (PWDOWN) is expressed in milliseconds and depends on the features of your target board. Make sure to choose a value large enough to ensure that the  $V_{\scriptscriptstyle DD}$  signal reaches the low logic level within the specified time. Note that, if the  $V_{DD}$  line has a high load, a longer time is required for the  $V_{DD}$  signal to reach the low logic level.

#### TPSETPAR RSTUP

Command syntax:

TCSETPAR RSTUP <time us>

Parameters:

time µs: Reset rising time, expressed in microseconds.

Description:

The Reset rising time (RSTUP) is expressed in microseconds and depends on the features of your target board. Make sure to choose a value large enough to ensure that the Reset signal reaches the high logic level within the specified time. Note that, if the Reset line has a high load, a longer time is required for the Reset signal to reach the high logic level. If RSTUP isn't long enough, FlashRunner could not be able to enter the SPI like programming mode.

#### **TPSETPAR RSTDOWN**

Command syntax:

TCSETPAR RSTDOWN <time µs>

Parameters:

time us: Reset falling time, expressed in microseconds.

Description:

The Reset falling time (RSTDOWN) is expressed in microseconds and depends on the features of your target board. Make sure to choose a value large enough to ensure that the Reset signal reaches the low logic level within the specified time. Note that, if the Reset line has a high load, a longer time is required for the Reset signal to reach the low logic level.

#### TCSETPAR SCLK

Command syntax:

TCSETPAR SCLK <frequency Hz>

Parameters:

frequency Hz: communication frequency, expressed in Hertz.

#### Description:

This command is used to set up the communication frequency between FlashRunner and target microcontroller. Must be lower than the FCPU.

## 4. Specific TPCMD Programming Commands

#### Overview

TPCMD commands perform a programming operation (i.e. mass erase, program, verify, etc.) These command must be sent within a TPSTART / TPEND command block.

Texas Instruments CC253x-specific target programming commands are the following:

| PCMD | UNLOCK: |

|------|---------|

|      | PCMD    |

TPCMD MASSERASE;

TPCMD BLANKCHECK;

TPCMD PROGRAM;

TPCMD VERIFY;

TPCMD READ;

TPCMD RUN.

#### **TPCMD UNLOCK**

Command syntax:

TPCMD UNLOCK

Description:

It unlocks and it erases all the Flash memory and the lock bits.

When the debug-lock bit, DBGLOCK, is set to 0, all debug commands except CHIP ERASE, READ STATUS, and GET CHIP ID are disabled. Note that after the debug-lock bit has changed due to a write to the lock-bit page or a CHIP\_ERASE command, the device must be reset to lock/unlock the debug interface. Issuing an UNLOCK command is the only way to clear the debug-lock bit, thereby unlocking the debug interface.

#### **TPCMD MASSERASE**

Command syntax:

TPCMD MASSERASE C

Command options:

C: Specifies (c) that this command refers to the whole Flash

memory, included the lock bits.

Description:

It erases all the Flash memory.

#### **TPCMD BLANKCHECK**

Command syntax:

TPCMD BLANKCHECK F <tgt start addr> <len>

Command parameters and options:

F: Specifies Flash (F) memory.

Device memory location from where the blankcheck tgt start address:

operation will start.

Number of locations to be blankchecked. len:

#### Description:

It blankchecks Flash memory. Blankchecks 1en locations starting from the address specified by tgt start address. The start address is the logical address specified in each single device datasheet or User's Guide under "Memory" chapter.

#### **TPCMD PROGRAM**

Command syntax:

TPCMD PROGRAM F <src offset> <tgt start addr> <len>

Command parameters and options:

F: Specifies Flash (F) memory.

src offset: Offset from the beginning of the source memory.

tgt start addr: Device memory location from where the program operation

will start.

Number of locations to be programmed. len:

Description:

It programs len locations of Flash memory starting from the tgt start addr address.

Flash memory is organized in 1024 or 2048 bytes pages; len specifies the number of locations to be programmed. tgt start addr is the logical address specified in each single device datasheet or User's Guide under "Memory" chapter.

#### **TPCMD VERIFY**

Command syntax:

TPCMD VERIFY F R <src offset> <tgt start addr> <len>

Command parameters and options:

**F**: Specifies Flash (**F**) memory.

R Specifies Readout (R).

src offset:

Offset from the beginning of the source memory.

tgt start addr: Device memory location from where the verify operation

will start.

len: Number of locations to be verified

#### Description:

It verifies len locations of Flash memory starting from the tgt start addr address. Flash memory is organized in 1024 or 2048 bytes pages; len specifies the number of locations to be verified.

#### **TPCMD READ**

Command syntax:

TPCMD READ F <tgt start addr> <len>

Command parameters and options:

F: Specifies Flash (F) memory.

tgt start addr: Device memory location from where the verify operation

will start.

len: Number of locations to be verified

via Giovanni Agnelli 1, 33083 Villotta di Chions (PN) Italy

Phone +39 0434 421111 - Fax +39 0434 639021 - info@smh-tech.com - www.smh-tech.com

#### Description:

It reads len locations of Flash memory starting from the tgt start addr address. Flash memory in reading operations is organized as 16-bit locations: internally the data to be read is mapped using the XDATA memory in the micro (XBANK, mapped in the area 0x8000-0xFFFF). 1en specifies the number of locations to be read.

## **TPCMD RUN**

Command syntax:

TPCMD RUN

Command parameters:

None.

Description:

It runs the target application.

## 5. Typical Programming Flow

The following flow chart illustrates typical steps to help you write your own script file.

## 6. Script Example

The example below shows a typical programming flow for a Texas Instruments CC253x device.

```

; FLASHRUNNER SCRIPT EXAMPLE FOR TI CC2533F96

; Use this example as a starting point for your specific programming needs

; Hardware connections

; DIOO (RESET_N: Reset)

; DIO1 (P2.2 - DCLK: Debug Clock)

; DIO2 (P2.1 - DD: Debug Data)

; Turns off logging

#LOG_OFF

; Halt on errors

#HALT_ON FAIL

; Sets device

TCSETDEV TI CC2533F96 TI_C

; Target voltage, mV (change as needed)

TCSETPAR VDD 3600

; VDD rise-time, ms (from 0 ms to 65535 ms)

TCSETPAR PWUP 10

; VDD fall-time, ms (from 0 ms to 65535 ms)

TCSETPAR PWDOWN 10

; RESET up time (from 0 us to 65535 us)

TCSETPAR RSTUP 100

; RESET down time (from 0 us to 65535 us)

TCSETPAR RSTDOWN 100

; SPI Like Debug interface frequency, Hz (change as needed)

```

| ; For this device the maximum debug clock frequency is 12 MHz             |

|---------------------------------------------------------------------------|

| TCSETPAR SCLK 12000000                                                    |

|                                                                           |

| ;                                                                         |

| Programming operation                                                     |

| ;                                                                         |

| ; Starts programming block                                                |

| TPSTART                                                                   |

|                                                                           |

| ; Image file to be programmed (must be placed in the \BINARIES directory) |

| TPSETSRC FILE TEST.FRB                                                    |

|                                                                           |

| ; Unlocks the debug port and mass erases the whole memory                 |

| TPCMD UNLOCK                                                              |

|                                                                           |

| ; Mass erases the whole memory                                            |

| TPCMD MASSERASE C                                                         |

|                                                                           |

| ; Blankchecks code memory (change addresses and length as needed)         |

| TPCMD BLANKCHECK F \$0 98304                                              |

| ; Programs code memory (change addresses and length as needed)            |

| TPCMD PROGRAM F \$0 \$0 98304                                             |

|                                                                           |

| ; Verifies code memory (change addresses and length as needed)            |

| TPCMD VERIFY F R \$0 \$0 98304                                            |

|                                                                           |

| ; Ends programming block                                                  |

| TPEND                                                                     |

|                                                                           |

The FlashRunner's system software setup will install script examples specific for each device of the CC253x family on your PC.

## 7. Programming Times

The following table shows programming times for selected Texas Instruments CC253x devices.

| Device     | Mem. Size   | Conditions               | Operations                          | Time    |

|------------|-------------|--------------------------|-------------------------------------|---------|

| CC2530F256 | 256KB Flash | FR01LAN,<br>SCLK=6,25MHz | Erase+Blankcheck+Program<br>+Verify | 25,83 s |

| CC2530F256 | 256KB Flash | FR04A16,<br>SCLK=6,25MHz | Erase+Blankcheck+Program<br>+Verify | 25,85 s |

Programming times depend on Programming Algorithm version, target board connections, communication mode, target microcontroller mask, and other conditions. Programming times for your actual system may therefore be different than the ones listed here. SMH Technologies reserves the right to modify Programming Algorithms at any time.

### 8. References

FlashRunner User's Manual.

Microcontroller-specific Datasheets and User's Guides.