Interfacing FlashRunner 2.0 with INFINEON TRAVEO2

07/03/2025 Driver v. 5.12 Moreno Ortolan

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

# ѕмн

## **INFINEON TRAVEO2 Introduction**

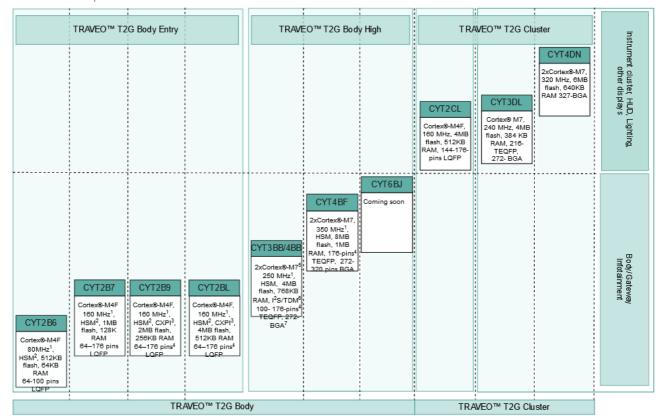

## 32-bit TRAVEO™ T2G Arm® Cortex® Microcontroller

The Infineon TRAVEO<sup>™</sup> T2G microcontrollers are based on the Arm<sup>®</sup> Cortex<sup>®</sup>-M4(Single core)/M7(Single core/Dual core) core and deliver high performance, enhanced human-machine interfaces, high-security and advanced networking protocols tailored for a broad range of automotive applications such as electrification, body control modules, gateway, and infotainment applications.

Based on the powerful Arm<sup>®</sup> Cortex<sup>®</sup> M series core in single and dual core operation it offers state-of-the-art real time performance, safety and security features. Infineon TRAVEO<sup>™</sup> T2G MCUs are used in motor control for hybrid and electric vehicles (HEV/EV), body electronics.

Infineon TRAVEO<sup>™</sup> T2G family builds upon the successful TRAVEO<sup>™</sup> T1G families.

The family supports the latest in-car networks, offers high performance function optimized for a minimum memory footprint and embeds dedicated features to increase data security in the car.

- 32-bit TRAVEO™ T2G Arm<sup>®</sup> Cortex<sup>®</sup> for Body

- > Overview

- > TRAVEO<sup>™</sup> T2G CYT4BF Series

- > TRAVEO<sup>™</sup> T2G CYT3BB/CYT4BB Series

- → TRAVEO<sup>™</sup> T2G CYT2BL Series

- > TRAVEO™ T2G CYT2B9 Series

- > TRAVEO<sup>™</sup> T2G CYT2B7 Series

> TRAVEO<sup>™</sup> T2G CYT2B6 Series

- 32-bit TRAVEO<sup>™</sup> T2G Arm<sup>®</sup> Cortex<sup>®</sup> for Cluster

- > Overview

- > TRAVEO™ T2G CYT2CL

- > TRAVEO™ T2G CYT3DL

- > TRAVEO<sup>™</sup> T2G CYT4DN

TRAVEO<sup>™</sup> T2G portfolio overview

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021

#### →smh-tech.com

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## 32-bit TRAVEO™ T2G Arm® Cortex® for Body

TRAVEO™ T2G for automotive body electronics applications offers cutting-edge performance, safety, and security features.

| 32-bit TRAVEO™ T2G Arm® Cortex® for Body subcategories |                                         |

|--------------------------------------------------------|-----------------------------------------|

| > TRAVEO <sup>™</sup> T2G CYT4BF Series                | > TRAVEO <sup>™</sup> T2G CYT2B9 Series |

| > TRAVEO™ T2G CYT3BB/CYT4BB Series                     | > TRAVEO™ T2G CYT2B7 Series             |

| > TRAVEO™ T2G CYT2BL Series                            | > TRAVEO™ T2G CYT2B6 Series             |

|                                                        |                                         |

The TRAVEO<sup>™</sup> T2G connected ready MCU family is designed for the smart world. The family offers wide scalability and network connectivity built into a single Arm<sup>®</sup> Cortex<sup>®</sup>- M4 and dual Cortex<sup>®</sup>- M7.

Performance has also been enhanced from 400 DMIPS in TRAVEO<sup>™</sup> T1G, to 1500 DMIPS in TRAVEO<sup>™</sup> T2G.

The TRAVEO<sup>™</sup> T2G for body electronics applications also provides scalability across memory size and pin count. The IP compatibility enables customers to design and develop their systems with a single-platform MCU solution.

TRAVEO<sup>™</sup> T2G devices have advanced security features with the introduction of HSM (Hardware security module), dedicated Cortex<sup>®</sup>-M0+ for secure processing, and embedded flash in dual bank mode for FOTA requirements.

The body family also features six power modes that enable ECUs to minimize overall power consumption.

Our MCUs come with an optimized software platform that is available for AUTOSAR MCAL (Microcontroller Abstraction Layer), self-test libraries, Flash EEPROM emulation, as well as security low-level drivers, combined with third-party firmware.

#### TRAVEO<sup>™</sup> T2G Arm<sup>®</sup> Cortex<sup>®</sup> for Body portfolio

|                                                                                                          | RAVEO™ T2G CYT26                                                                | RAVEO™ T2G CYT2B                                                                       | T<br>RAVEO™ T2G CYT2BL                                                               | AVEO <sup>™</sup> T2G CYT3/4E<br>2xCortex®-M7, 250 MHz,<br>ASIL-B, HSM,<br>4MBflash, 768KB RAM,<br>eMMC, ethernet, I2S/TDM<br>100-176-pins TEQFP,<br>272-ball BGA | ASIL-D, HSM,<br>8MBflash, 1024KB RAM,<br>eMMC, ethernet, FlexRay,<br>I2S/TDM 176-pins |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| TRAVEO™ T2G CYT2B<br>Cortex®-M4, 80 MHz,<br>ASIL-B, HSM,<br>512KB flash,<br>64KB RAM<br>64-100 pins LQFP | Cortex®-M4, 160 MHz,<br>ASIL-B, HSM,<br>1MB flash, 128K RAM<br>64–176 pins LQFP | Cortex®-M4, 160 MHz,<br>ASIL-B, HSM, CXPI<br>2MB flash, 256KB RAM,<br>64–176 pins LQFP | Cortex®-M4,160 MHz,<br>ASIL-B, HSM, CXPI<br>4MB flash, 512KB RAM<br>64–176 pins LQFP |                                                                                                                                                                   |                                                                                       |

|                                                                                                          | TRAVEO™ T2G I                                                                   | Body Entry MCU                                                                         |                                                                                      | TRAVEO™ T2G B                                                                                                                                                     | ody High End MCU                                                                      |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## 32-bit TRAVEO™ T2G Arm® Cortex® for Cluster

TRAVEO™ T2G Instrument Cluster offers high display resolution, superior performance and multiple displays with dynamic content. All while using less power and less memory.

32-bit TRAVEO™ T2G Arm® Cortex® for Cluster subcategories

> TRAVEO™ T2G CYT2CL

> TRAVEO™ T2G CYT4DN

> TRAVEO™ T2G CYT3DL

TRAVEO<sup>™</sup> T2G automotive microcontrollers (MCU) family for Instrument Cluster with its new graphics architecture enables a more robust and feature-rich graphics engine for automotive display systems.

The product families provide the most extensive scalability, covering the conventional gauge instrument cluster, hybrid instrument cluster, and virtual instrument cluster.

The option of line-based operation of the graphics engine within the microcontroller minimizes the memory required for graphics processing. With the optimized 2.5D graphics engine and extended density of embedded Flash and Video RAM, TRAVEO<sup>™</sup> T2G graphic MCU can support the virtual instrument cluster with high resolution up to 2880 x 1080.

TRAVEO™ T2G Instrument Cluster family eliminates bulky energy-hungry thermo-mechanical designs with a single platform MCU solution.

It further removes costs with innovative on-the-fly-based rendering in the integrated VRAM.

This growing family of high-performance MCUs is scalable and comes with varying configurations of ARM<sup>\*</sup> Cortex<sup>\*</sup> CPUs.

#### TRAVEO<sup>™</sup> T2G Arm<sup>®</sup> Cortex<sup>®</sup> for Cluster portfolio

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

## **INFINEON TRAVEO2 Protocol and PIN map**

**TRAVEO2** devices support the SWD protocol.

**#TCSETPAR** CMODE <SWD>

#### **INFINEON TRAVEO2 PIN MAP**

| 🔋 Pin | Мар Тоо |            |         |         |       |         |         |            |         |            |                |            |         |         |      |            |            |        |           |            |         |    |            |          |   |              |          |   |   |   |   | -    |        | ×      |

|-------|---------|------------|---------|---------|-------|---------|---------|------------|---------|------------|----------------|------------|---------|---------|------|------------|------------|--------|-----------|------------|---------|----|------------|----------|---|--------------|----------|---|---|---|---|------|--------|--------|

| Sele  | t your  | Flash      | Runn    | er mo   | odel: | FR 2    | 2.0     |            |         |            |                |            |         |         |      |            |            |        |           |            |         |    |            |          |   |              |          |   |   |   |   | Expo | ort to | PDF    |

|       |         |            |         |         |       |         |         |            |         |            |                |            | Mas     | ter b   | oard | l con      | nect       | tor (( | <b>.1</b> | - Ch       | .8)     |    |            |          |   |              |          |   |   |   |   |      |        | Γ.     |

|       |         | _          | _       | _       | _     | _       | _       | _          | _       | _          | _              | _          | _       | _       | _    | _          | _          | _      | _         | _          | _       | _  | _          | _        | _ | _            | _        | _ | _ | _ | - |      | 7      |        |

| Ĩ     |         |            |         |         |       |         |         |            |         |            |                |            |         |         |      |            |            |        |           |            |         |    |            |          |   |              |          |   |   |   |   |      | ٦      | С<br>В |

|       |         |            |         |         |       |         |         |            |         |            |                |            |         |         |      |            |            |        |           |            |         |    |            |          |   |              |          |   |   |   |   |      |        | А      |

|       | 32      | <b>3</b> 1 | ∎<br>30 | ∎<br>29 | 28    | ∎<br>27 | ∎<br>26 | <b>2</b> 5 | ∎<br>24 | <b>2</b> 3 | <b>1</b><br>22 | <b>2</b> 1 | ∎<br>20 | ∎<br>19 | 18   | <b>1</b> 7 | <b>1</b> 6 | 15     | ∎<br>14   | <b>1</b> 3 | ∎<br>12 | 11 | <b>1</b> 0 | <b>9</b> | 8 | 7            | <b>6</b> | 5 | 4 | 3 | 2 | 1    |        |        |

| Sele  | t a cha | innel:     |         |         |       |         |         |            |         |            |                |            |         |         |      |            | Co         | nnect  | ion d     | escri      | ptions  | :  |            |          |   |              |          |   |   |   |   |      |        |        |

|       | Ch.1 -  |            |         | ]) A[   | SWD   | )       |         |            |         |            |                |            |         |         |      |            | C          | DIO1:  |           |            |         |    |            |          |   | Pin:<br>Pin: |          |   |   |   |   |      |        |        |

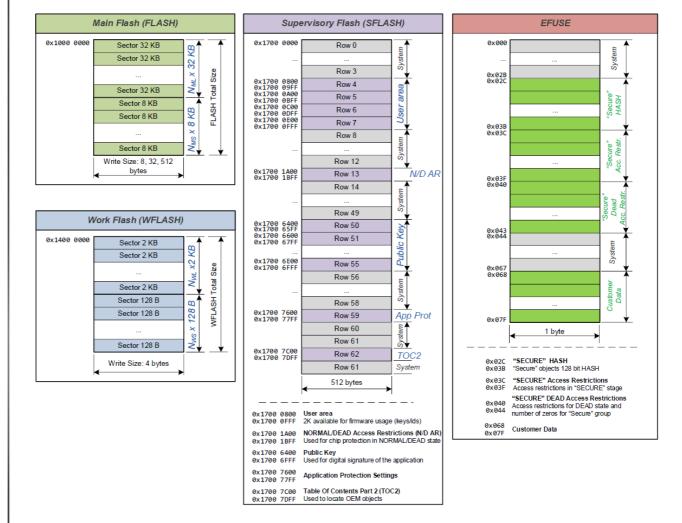

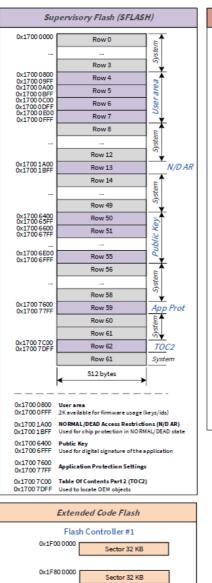

## **INFINEON TRAVEO2 Memory Map**

| Memory Type                               | Start Address | End Address | Memory Size | Page Size | Blank Value | Address Unit |

|-------------------------------------------|---------------|-------------|-------------|-----------|-------------|--------------|

| [F] - Main Flash                          | 0x10000000    | 0x1082FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| [E] - Work Flash                          | 0x14000000    | 0x1403FFFF  | 256.00 KiB  | 4         | 0xFF        | BYTE         |

| [S] - Supervisory Flash                   | 0x17000000    | 0x17007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| [C] - Checksum (reserved virtual address) | 0x90300000    | 0x90300001  | 2 Byte      | 0         | 0xFF        | BYTE         |

| [M] - Metadata (reserved virtual address) | 0x90500000    | 0x9050000B  | 12 Byte     | 0         | 0xFF        | BYTE         |

| [P] - eFUSE (virtual address)             | 0x90700000    | 0x907003FF  | 1.00 KiB    | 1         | 0x00        | BYTE         |

| evice:<br>amily:<br>anufacturer:<br>Igorithm: | CYT4BFBCJA<br>CYT4BF<br>INFINEON<br>TRAVEO2 - libtraveo2.so |                 |             |             |           |             |              |

|-----------------------------------------------|-------------------------------------------------------------|-----------------|-------------|-------------|-----------|-------------|--------------|

|                                               | Метогу Туре                                                 | Start Address * | End Address | Memory Size | Page Size | Blank Value | Address Unit |

| 1 [F] - Main                                  | Flash                                                       | 0x1000000       | 0x1082FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| 2 [E] - Work                                  | : Flash                                                     | 0x14000000      | 0x1403FFFF  | 256.00 KiB  |           | 0xFF        | BYTE         |

| 3 [S] - Supe                                  | rvisory Flash                                               | 0x17000000      | 0x17007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| 4 [C] - Chee                                  | ksum (reserved virtual address)                             | 0x90300000      | 0x90300001  | 2 Byte      |           | 0xFF        | BYTE         |

| 5 [M] - Met                                   | adata (reserved virtual address)                            | 0x90500000      | 0x9050000B  | 12 Byte     |           | 0xFF        | BYTE         |

| 6 [P] - eFus                                  | e (virtual address)                                         | 0x90700000      | 0x907003FF  | 1.00 KiB    |           | 0x00        | BYTE         |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

## UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

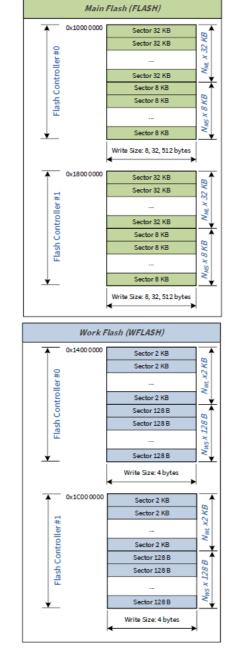

## **INFINEON TRAVEO2 Memory Map for Dual Controller Devices**

| Memory Type                               | Start Address | End Address | Memory Size | Page Size | Blank Value | Address Unit |

|-------------------------------------------|---------------|-------------|-------------|-----------|-------------|--------------|

| [F] - Main Flash                          | 0x10000000    | 0x1082FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| [E] - Work Flash                          | 0x14000000    | 0x1403FFFF  | 256.00 KiB  | 4         | 0xFF        | BYTE         |

| [S] - Supervisory Flash                   | 0x17000000    | 0x17007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| [F] - Main Flash                          | 0x18000000    | 0x1882FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| [E] - Work Flash                          | 0x1C000000    | 0x1C03FFFF  | 256.00 KiB  | 4         | 0xFF        | BYTE         |

| [T] - Extended Code Flash                 | 0x1F000000    | 0x1F007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| [T] - Extended Code Flash                 | 0x1F800000    | 0x1F807FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| [C] - Checksum (reserved virtual address) | 0x90300000    | 0x90300001  | 2 Byte      | 0         | 0xFF        | BYTE         |

| [M] - Metadata (reserved virtual address) | 0x90500000    | 0x9050000B  | 12 Byte     | 0         | 0xFF        | BYTE         |

| [P] - eFUSE (virtual address)             | 0×90700000    | 0×907003FF  | 1.00 KiB    | 1         | 0×00        | BYTE         |

#### 🚦 Memory Map Tool

|    |                    | CYT6BJBDHA<br>CYT6BJ<br>INFINEON<br>TRAVEO2 - libtrav | eo2.so          |             |             |           |             |              |

|----|--------------------|-------------------------------------------------------|-----------------|-------------|-------------|-----------|-------------|--------------|

|    | Me                 | етогу Туре                                            | Start Address 🛎 | End Address | Memory Size | Page Size | Blank Value | Address Unit |

| 1  | [F] - Main Flash   |                                                       | 0x1000000       | 0x1082FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| 2  | [E] - Work Flash   |                                                       | 0x14000000      | 0x1403FFFF  | 256.00 KiB  | 4         | 0xFF        | BYTE         |

| 3  | [S] - Supervisory  | <sup>7</sup> Flash                                    | 0x17000000      | 0x17007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| 4  | [F] - Main Flash   |                                                       | 0x18000000      | 0x1882FFFF  | 8.19 MiB    | 512       | 0xFF        | BYTE         |

| 5  | [E] - Work Flash   |                                                       | 0x1C000000      | 0x1C03FFFF  | 256.00 KiB  | 4         | 0xFF        | BYTE         |

| 6  | [T] - Extended C   | ode Flash                                             | 0x1F000000      | 0x1F007FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| 7  | [T] - Extended C   | ode Flash                                             | 0x1F800000      | 0x1F807FFF  | 32.00 KiB   | 512       | 0xFF        | BYTE         |

| 8  | [C] - Checksum     | (reserved virtual address)                            | 0x90300000      | 0x90300001  | 2 Byte      | 0         | 0xFF        | BYTE         |

| 9  | [M] - Metadata     | (reserved virtual address)                            | 0x90500000      | 0x9050000B  | 12 Byte     | 0         | 0xFF        | BYTE         |

| 10 | [P] - eFuse (virtu | ial address)                                          | 0x90700000      | 0x907003FF  | 1.00 KiB    | 1         | 0x00        | BYTE         |

#### Export to PDF

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## **INFINEON TRAVEO2 eFUSE**

This is an OTP area (One-Time-Programmable) and this means that once a bit is blown, so it has the '1' state, it cannot return to the '0' state.

Single eFUSE can be changed in state bit-by-bit by putting the value in .FRB file and using the program command.

Only bits that are different from '0' will be written because the original state of a bit of eFUSE is '0' and then can become '1' by blowing.

If an eFUSE byte (different from 0x0 and 0xFF) is on the FRB file but the target device has already that byte written, the eFUSE is **NOT blown another time**.

If an eFUSE byte (different from 0x0 and 0xFF) is on .FRB file but it is different from eFUSE byte read from device, only '1' bits will be written.

After programming (blowing process) a check operation (verify) checks byte-by-byte the eFUSE area, comparing .FRB eFUSE values with current device values read from eFUSE area.

The driver writes bit-by-bit the eFUSE value but the minimum blowing size is the value of **1 byte** in .FRB file, this means that in the .FRB you have to consider the entire 8-bit value of eFUSE.

Since the eFUSE area is not accessed via the address space then FlashRunner refers to a virtual address which is declared in the programming specification of Infineon. This address starts from 0x90700000 up to 0x907003FF and corresponds to the eFUSE **bit** area (**not byte area**).

According to specifications, each eFUSE byte is made up of 8 eFUSEs bits and each location of the virtual address space corresponds to the eFUSEs bit to be programmed. Please see Infineon's programming specifications to better understand how eFUSE memory area works.

## **INFINEON TRAVEO2 Single Bank and Dual Bank**

Traveo II has Single Bank and Dual Bank options.

In **Single Bank Mode** the Cortex core of the device has direct access to all the flash memory which is seen as a single continuous portion of the address space.

In other words, the flash is seen as a single block.

In **Dual Bank Mode** the memory is divided into two banks, which cannot be accessed directly and immediately because before the user has to select the bank to use.

For command specifications please refer to the **#TCSETPAR** FLASH\_BANK\_MODE or **#TCSETPAR** WORKFLASH\_BANK\_MODE description.

Once the bank has been selected, the user is allowed to program it. Since the memory is not now a single block, the user has to use an FRB with half data and then the complete memory size.

The double bank option is a good way to introduce OTA updates because you can change the whole content of one bank.

Traveo II devices are very flexible thanks to the possibility of releasing OTA updates. When you have to make an OTA update or in general firmware update of a microcontroller it means you want to rewrite a part of the flash.

The part you want to rewrite will have a new firmware which will be the one used as the main execution firmware. However, it could happen that during the update the microcontroller turns off and corrupts the entire system.

To solve this problem, a second image (default image) is used, consisting of software that is used in the event of an emergency when the main updatable image has been corrupted. Hence the need to execute, if necessary, a second image which serves to restore the first image.

NOTE: For further information refer to the document AN229058 on Infineon's website.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## **INFINEON TRAVEO2 SWD and JTAG Locking**

In Traveo II devices there is the possibility to lock permanently the DAP (Debug Access Port) of the SWD/JTAG. This operation is irreversible and once the DAP is disabled, it is no longer possible to connect with the device.

To disable the DAP, it is necessary to set the **TOC2\_FLAGS** which are 2 bytes located at the memory address **0x17007DF8** of the Supervisory Flash.

To lock the device, you can use the command **#TPCMD** PATCH\_SUPERVISORY\_MEMORY. Please refer to the command description.

Here are the TOC2\_FLAGS:

| Bit           | Name              | Description                                                                                                                                                                                                                                                                                                                       |

|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit [1:0]     | CLOCK_CONFIG      | Indicates clock frequency configuration. The clock should stay the same after Flash boot<br>execution<br>0 = 8 MHz, IMO, no FLL<br>1 = 25 MHz IMO + FLL<br>2 = 50 MHz IMO + FLL<br>3 = Use ROM boot clock configuration                                                                                                           |

| bit [4:2]     | LISTEN_WINDOW     | Determines the Listen window to allow sufficient time to acquire debug port.<br>0 = 20 ms (Default)<br>1 = 10 ms<br>2 = 1 ms<br>3 = 0 ms (No Listen window)<br>4 = 100 ms                                                                                                                                                         |

| bit [6:5]     | SWJ_PINS_CTL      | Determines if SWJ pins are configured in SWJ mode by Flash boot.<br>0 = Do not enable SWJ pins in Flash boot. Listen window is skipped<br>1 = Do not enable SWJ pins in Flash boot. Listen window is skipped<br>2 = Enable SWJ pins in Flash boot (default)<br>3 = Do not enable SWJ pins in Flash boot. Listen window is skipped |

| bit [8:7]     | APP_AUTH_CTL      | Determines if the application image digital signature verification (authentication) is<br>performed:<br>0 = Authentication is enabled (default)<br>1 = Authentication is disabled<br>2 = Authentication is enabled (recommended)<br>3 = Authentication is enabled                                                                 |

| bit<br>[10:9] | FB_BOOTLOADER_CTL | Determine if the internal bootloader in Flash boot is disabled:<br>0 = Internal bootloader is disabled<br>1 = Internal bootloader is launched if the other bootloader conditions are met (default)<br>2 = Internal bootloader is disabled<br>3 = Internal bootloader is disabled.                                                 |

Set LISTEN\_WINDOW = 3 to disable the listening window of time to acquire the device in SWD or JTAG protocol.

Set **SWJ\_PINS\_CTL** = 0 to disable SWD or JTAG pin function (dedicated for debugging and flashing) after the Flash Boot has been executed.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## **INFINEON TRAVEO2 Driver Parameters**

The standard parameters are used to configure some specific options inside TRAVEO2 driver.

## **#TCSETPAR ENTRY\_CLOCK**

| Syntax: | #TCSETPAR | ENTRY  | CL  |

|---------|-----------|--------|-----|

| Syntax: | #TCSETPAR | ENTRY_ | _CT |

OCK <Frequency>

Accepted parameters 4000000, 2000000, 1000000, 500000, 100000 Hz <Frequency> Description: Set the JTAG/SWD frequency used in the Connect procedure before raising the PLL of the device, if the device

PLL is available Note: Default value 1.00 MHz

#### **#TCSETPAR ACQUIRING\_SEQUENCE**

| Syntax:                 | <b>#TCSETPAR</b> ACQUI                                                                | IRING_SEQUENCE                              |                                                                                                               |                                            |

|-------------------------|---------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Description:            | The acquiring chip<br>Traveo II devices<br>The <i>ACQUIRE_CH</i><br>FlashRunner and t | //Pis a procedure that use he target device | by Infineon and you can find the<br>s the reset line to establish the c<br>RE_CHIP does not use the reset lin |                                            |

| Note:                   | By default, the driv                                                                  | ver uses the ACQUIRE_C                      | HIP method                                                                                                    |                                            |

| #TCSETPAI               | R BLANKCHE                                                                            | CK_IN_PROGRAM                               | /I_FLASH                                                                                                      |                                            |

| Syntax:                 | <b>#TCSETPAR</b> BLANH                                                                | KCHECK_IN_PROGRAM_FL                        | ASH <value></value>                                                                                           |                                            |

|                         | <value></value>                                                                       | Accepted values are Yes                     | or No                                                                                                         |                                            |

| Description:            | There are two pos<br>The first choice is                                              | sible ways to perform the to perform the    | on the Main Flash memory<br>e blankcheck operation<br>I #TPCMD BLANKCHECK F<br>ion during the #TPCMD PROGRA   | M F command                                |

| Note:                   | None                                                                                  |                                             |                                                                                                               |                                            |

| #TCSETPAI               | R BLANKCHE                                                                            | CK_IN_PROGRAM                               | /I_WFLASH                                                                                                     |                                            |

| Syntax:                 | <b>#TCSETPAR</b> BLANN                                                                | KCHECK_IN_PROGRAM_WF                        | LASH <value></value>                                                                                          |                                            |

|                         | <value></value>                                                                       | Accepted values are Yes                     | or No                                                                                                         |                                            |

| Description:            | There are two pos<br>The first choice is                                              | sible ways to perform the to perform the    | on the Work Flash memory<br>e blankcheck operation<br>I #TPCMD BLANKCHECK E<br>ion during the #TPCMD PROGRA   | M E command                                |

| Note:                   | None                                                                                  |                                             |                                                                                                               |                                            |

|                         |                                                                                       |                                             |                                                                                                               |                                            |

|                         |                                                                                       |                                             |                                                                                                               |                                            |

|                         |                                                                                       |                                             |                                                                                                               |                                            |

|                         |                                                                                       |                                             |                                                                                                               | UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING |

| ) and Pagistarad Office | Canitala                                                                              | sociale £102 040                            | D-U-N-S <sup>®</sup> 51-724-9350                                                                              | -> smb-tech com                            |

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 **REA** PN-97255

## **#TCSETPAR EFUSE\_MARGIN\_LEVEL**

| Syntax:      | <b>#TCSETPAR</b> EFUSE_MARGIN_LEVEL <nominal_resistance low_resistance high_resistance></nominal_resistance low_resistance high_resistance>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | NOMINAL_RESISTANCE $\rightarrow$ default read condition<br>LOW_RESISTANCE $\rightarrow$ -50% from nominal resistance<br>HIGH_RESISTANCE $\rightarrow$ +50% from nominal resistance                                                                                                                                                                                                                                                                                                                                                                                          |

| Description: | This command is used to in order to define the Margin Verify mode for the eFUSE<br>The margin verify is available only for the eFUSE memory area<br>This verification procedure differs from the classic one in re-reading the values stored in the memory by<br>changing certain levels of current and supply voltage of the flash memory<br>This allows greater reliability as the data are read back in power range conditions other than the typical ones<br>The procedure provided by Infineon is carried out automatically by the HW of the device during the writing |

| Note:        | All other information regarding this command is <b>Under NDA</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **#TCSETPAR FLASH\_BANK\_MODE**

Syntax: **#TCSETPAR** FLASH\_BANK\_MODE <**SINGLE\_BANK|DUAL\_BANK\_MAPPING\_A|DUAL\_BANK\_MAPPING\_B**>

*Description:* This command enables the dual bank mode if you select the DUAL\_BANK\_MAPPING\_A or B parameter

The Main Flash memory area supports the dual bank mode and when this option is selected the flash memory region is split into two half banks

One is called Logical Bank 0 and the other is called Logical Bank 1

On the below chapter Single Bank and Dual Bank Overview there is an explanation of the dual bank mode application

DUAL\_BANK\_MAPPING\_A

The data to be programmed have to be half the total size of the Main Flash.

For this example, we have to program data from 0x10000000 to 0x103F7FFF (for the large sectors) and from 0x103F8000 to 0x10417FFF.

Following this example, the memory programmed will be the green one:

| _          |                                | 0x1083_0000         |

|------------|--------------------------------|---------------------|

| 32 × 8KB   | Code Region<br>(Small sectors) | 0x107F 0000         |

| 254 × 32KB | Code Region<br>(Large sectors) | <u>0x1000_0</u> 000 |

DUAL\_BANK\_MAPPING\_B

The data to be programmed have to be half the total size of the Main Flash.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

SMH Technologies S.r.l.

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S\* 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

For this example, we have to program data from 0x10000000 to 0x103F7FFF (for the large sectors) and from 0x103F8000 to 0x10417FFF.

Following this example, the memory programmed will be the blue one:

|                                    | 0x1083_0000 |

|------------------------------------|-------------|

| B Code Region<br>X (Small sectors) |             |

|                                    | 0x107F_0000 |

| Code Region<br>(Large sectors)     | 0×1000_0000 |

#### DUAL\_BANK\_MAPPING\_BOTH\_A\_AND\_B

The data to be programmed have to be half the total size of the Main Flash.

For this example, we have to program data from 0x10000000 to 0x103F7FFF (for the large sectors) and from 0x103F8000 to 0x10417FFF.

Following this example, the memory programmed will be both green and blue. The difference from a normal program is that the green part will contain the original data and the blue part will contain an exact copy.

#### **#TCSETPAR WORKFLASH\_BANK\_MODE**

Syntax: #TCSETPAR WORKFLASH BANK MODE <SINGLE\_BANK/DUAL\_BANK\_MAPPING\_A/DUAL\_BANK\_MAPPING\_B>

Description: This command enables the dual bank mode if you select the DUAL\_BANK\_MAPPING\_A or B parameter

The Work Flash memory area supports the dual bank mode and when this option is selected the flash memory region is split into two half banks

One is called Logical Bank 0 and the other is called Logical Bank 1

In the below chapter Single Bank and Dual Bank Overview there is an explanation of the dual bank mode application

#### DUAL\_BANK\_MAPPING\_A

The data to be programmed have to be half the total size of the Work Flash.

For this example, we have to program data from 0x14000000 to 0x1400BFFF (for the large sectors) and from 0x1400C000 to 0x14010000.

Following this example, the memory programmed will be the green one:

**SMH** Technologies

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

|           |                                | 0x1402_0000 |

|-----------|--------------------------------|-------------|

| 256×128 B | Work Region<br>(Small sectors) | 0x1401_8000 |

| 48 × 2 KB | Work Region<br>(Large sectors) |             |

|           |                                | 0x1400_0000 |

#### DUAL\_BANK\_MAPPING\_B

The data to be programmed have to be half the total size of the Work Flash.

For this example, we have to program data from 0x14000000 to 0x1400BFFF (for the large sectors) and from 0x1400C000 to 0x14010000.

Following this example, the memory programmed will be the blue one:

| _           |                                | 0x1402_0000 |

|-------------|--------------------------------|-------------|

| 256 × 128 B | Work Region<br>(Small sectors) | 0x1401_8000 |

| 48×2 KB     | Work Region<br>(Large sectors) |             |

|             |                                | 0x1400_0000 |

#### DUAL\_BANK\_MAPPING\_BOTH\_A\_AND\_B

The data to be programmed have to be half the total size of the Work Flash.

For this example, we have to program data from 0x14000000 to 0x1400BFFF (for the large sectors) and from 0x1400C000 to 0x14010000.

Following this example, the memory programmed will be the both the green and the blue.

The difference from a normal program is that the green part will contain the original data and the blue part will contain an exact copy.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## **#TCSETPAR SAMPLING\_POINT**

| Syntax:      | <b>#TCSETPAR</b> SAMPLING_POINT <value></value> |                                                                                                       |  |  |

|--------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

|              | <value></value>                                 | Accepted values are in the range 1-15                                                                 |  |  |

| Description: | •                                               | er to permanently set the sampling point of the f<br>d to leave this parameter with the default value |  |  |

| Note:        | Default value 17                                |                                                                                                       |  |  |

**INFINEON TRAVEO2 Driver Commands**

Here you can find the complete list of all available commands for TRAVEO2 driver.

→ Main Flash Work Flash E → → Supervisorv Flash S т → Extended Code Flash → Checksum (reserved virtual address) On this virtual memory area is stored the checksum of the firmware С → Metadata (reserved virtual address) On this virtual memory area is stored the Silicon ID and other relevant data М Р → eFUSE (virtual address) External Memory (Hyper mory or generic external memory connected to Traveo II device

FPGA

Traveo 2 devices with one Flash Controller:

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

#### UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

SMH

#### Traveo 2 devices with two Flash Controller:

Write Size: 8, 32, 512 bytes

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021

## UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

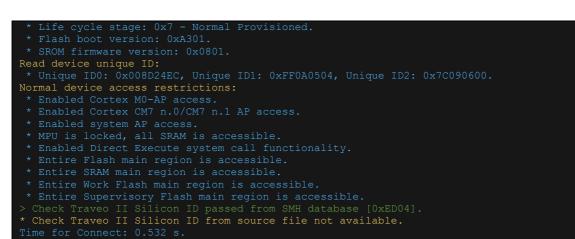

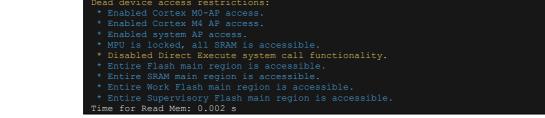

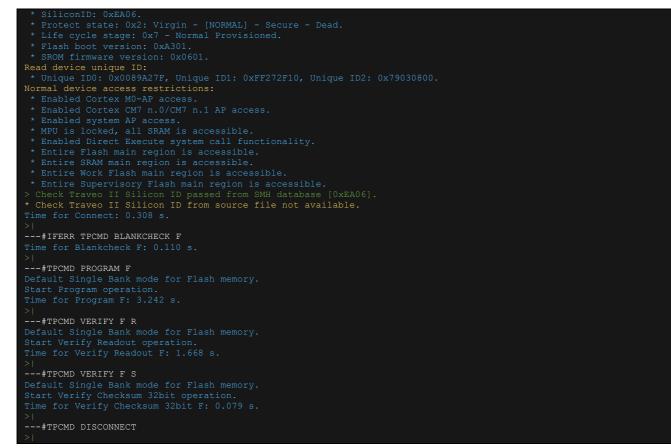

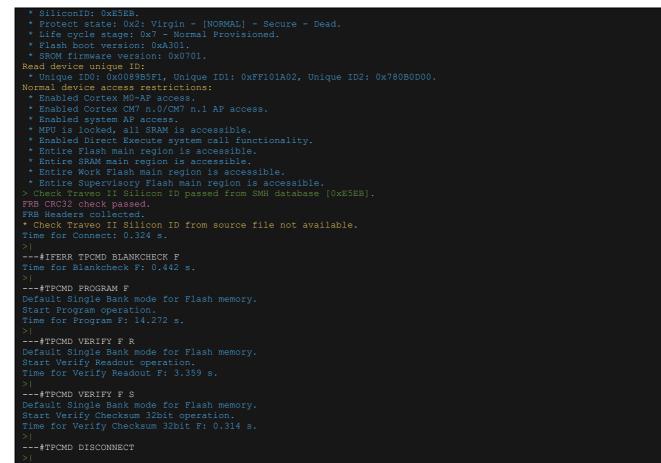

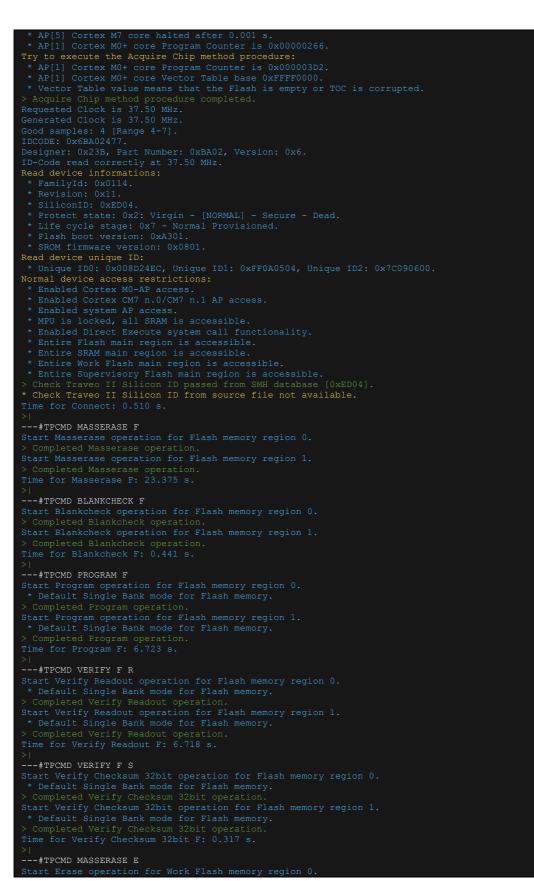

## **#TPCMD CONNECT**

#### **#TPCMD** CONNECT

---#TPCMD CONNECT Protocol selected SWD.

This function performs the entry and is the first command to be executed when starting the communication with the device. There are two types of connect, regarding this please read **#TCSETPAR** ACQUIRING\_SEQUENCE. Here you see can the log of a standard connect with the Acquire Chip procedure selected:

Connect procedure when the device is blank:

IDR: 0x84770001, Type: AMBA AHB3 bus. AP[2] AP[4] IDR: 0x84770001, Type: AMBA AHB3 bus. AP[5] IDR: 0x84770001, Type: AMBA AHB3 bus. AP[1] Cortex M0+ core Program Counter is 0x000003D2. \* AP[1] Cortex M0+ core Program Counter is 0x00000214. Try to halt the Cortex M7 core: \* AP[1] Cortex M0+ core Program Counter is 0x0000024E. Try to halt the Cortex M7 core: Cortex M0+ core Program Counter is 0x00000258 to execute the Acquire Chip method procedure: Requested Clock is 37.50 MHz.

#### →smh-tech.com

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 \* Enabled system AP access.

\* MPU is locked, all SRAM is accessible.

\* Enabled Direct Execute system call functionality.

\* Entire Flash main region is accessible.

\* Entire SRAM main region is accessible.

\* Entire Work Flash main region is accessible.

\* Entire Supervisory Flash main region is accessible.

> Check Traveo II Silicon ID passed from SMH database [0xED04].

\* Check Traveo II Silicon ID from source file not available.

Connect procedure when the device is already programmed:

-#TPCMD CONNECT

```

Toggling XRES pin to execute Acquire Chip procedure.

Scanning AP map to find all APS:

* AP[0] IDR: 0x84770001, Type: AMBA AHB3 bus.

* AP[1] IDR: 0x84770001, Type: AMBA AHB3 bus.

* AP[2] IDR: 0x84770001, Type: AMBA AHB3 bus.

* AP[3] IDR: 0x84770001, Type: AMBA AHB3 bus.

* AP[4] IDR: 0x84770001, Type: AMBA AHB3 bus.

* AP[5] IDR: 0x84770001, Type: AMBA AHB3 bus.

AP[4] ARM - CPUID: 0x411FC272 - Found Cortex M7 revision r1p2.

AP[5] ARM - CPUID: 0x411FC272 - Found Cortex M7 revision r1p2.

Try to halt the Cortex M7 core:

* AP[1] Cortex M0+ core Program Counter is 0x0000024A.

Try to halt the Cortex M7 core:

AP[1] Cortex M0+ core Program Counter is 0x00000256

Iry to execute the Acquire Chip method procedure:

Trigger a software reset to restart CPU.

Reconnect and waiting for CPU to hit the breakpoint.

Requested Clock is 37.50 MHz.

Generated Clock is 37.50 MHz.

```

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy

Società Unipersonale

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

#### ID-Code read correctly at 1.00 MHz after 12 retries

This is normal behavior because when the Traveo2 device is powered on the SWD/JTAG port is not immediately available.

The TRAVEO2 driver tries to read the ID code several times before the SWD/JTAG port is activated.

#### Check Traveo II Silicon ID from source file not available

This warning means that the FRB file is not present or the Silicon ID is not available inside FRB file. Therefore, it is not possible to compare the Silicon ID read from the device with the one present in the file to be programmed.

#### **#TPCMD MASSERASE**

#### **#TPCMD** MASSERASE <F|E|X>

This function performs a masserase for Main Flash, Work Flash or External Memory.

#### **#TPCMD ERASE**

#### **#TPCMD** ERASE <F|E|X> <start address> <size>

This function performs a sector erase for the Main Flash, Work Flash or External Memory. Main Flash has several large 32KiB sectors and several small 16KiB sectors. The Work Flash has several large 2 KiB sectors and several small 128 B sectors. The driver automatically handles the erase of large and/or small sectors depending on the address and size inserted. In addition to this, the driver handles the alignment of Start address and Size if the inputs are not aligned to the memory granularity.

#### **#TPCMD BLANKCHECK**

#### **#TPCMD** BLANKCHECK <F|E|X>

Blankcheck is only available for Main Flash, Work Flash and External Memory. Verify if all memory is erased.

**#TPCMD** BLANKCHECK <F|E|X> <start address> <size>

Blankcheck is only available for Main Flash, Work Flash and External Memory. Verify if selected part of memory is erased. Enter the Start Address and Size in hexadecimal format.

#### **#TPCMD PROGRAM**

**#TPCMD** PROGRAM <F|E|S|P|X>

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

Program available for Main Flash, Work Flash, Supervisory Flash, eFUSE and External Memory. Programs all memory of the selected type based on the data in the FRB file.

The Supervisory Flash contains bytes whose value corresponds to the Traveo2 settings and protections. Writing random values in this area produces unpredictable results, so if you need to modify only some specific bits, please use the **#TPCMD** PATCH SUPERVISORY FLASH command.

The eFUSE is an OTP area (One-Time-Programmable) and once a byte is written it cannot be changed anymore. Note that both Supervisory Flash and eFUSE have zones that cannot be programmed.

#### **#TPCMD** PROGRAM <F|E|S|P|X> <start address> <size>

Program available for Main Flash, Work Flash, Supervisory Flash, eFUSE and External Memory. Programs selected part of memory of the selected type based on the data in the FRB file. Enter the Start Address and Size in hexadecimal format.

The Supervisory Flash contains bytes whose value corresponds to the Traveo2 settings and protections. Writing random values in this area produces unpredictable results, so if you need to modify only some specific bits, please use the **#TPCMD** PATCH SUPERVISORY FLASH command.

The eFUSE is an OTP area (One-Time-Programmable) and once a byte is written it cannot be changed anymore. Note that both Supervisory Flash and eFUSE have zones that cannot be programmed.

#### **#TPCMD VERIFY**

#### **#TPCMD** VERIFY <F|E|S|P> <R>

R: Readout Mode. Verify Readout available for Main Flash, Work Flash, Supervisory Flash and eFUSE. Verify all memory of the selected type based on the data in the FRB file.

#### **#TPCMD** VERIFY <F|E|S|P> <R> <start address> <size>

#### R: Readout Mode.

Verify Readout available for Main Flash, Work Flash, Supervisory Flash and eFUSE. Verify selected part of memory of the selected type based on the data in the FRB file. Enter the Start Address and Size in hexadecimal format.

#### **#TPCMD** VERIFY <F|E|S|P> <S>

S: Checksum 32 Bit Mode. Verify Checksum available for Main Flash, Work Flash, Supervisory Flash and eFUSE. Verify all memory of the selected type based on the data in the FRB file.

**#TPCMD** VERIFY <F|E|S|P> <S> <start address> <size>

S: Checksum 32 Bit Mode. Verify Checksum available for Main Flash, Work Flash, Supervisory Flash and eFUSE. Verify selected part of memory based on the data in the FRB file. Enter the Start Address and Size in hexadecimal format.

#### **#TPCMD VERIFY MARGIN EFUSE**

#### **#TPCMD** MARGIN VERIFY Margin Verify is available only for eFUSE memory.

Verify Margin of all eFUSEs.

**#TPCMD** MARGIN VERIFY <Virtual Start Address> <Virtual Size> Margin Verify is available only for eFUSE memory. Verify Margin selected part of eFUSEs.

#### **#TPCMD READ**

**#TPCMD** READ <F|E|S|P|X> **#TPCMD** READ <F|E|S|P|X> <start address> <size>

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

Capitale sociale €102.040 P.I. 01697470936 C.F.01697470936 **REA PN-97255**

D-U-N-S® 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

Read function for Main Flash, Work Flash, Supervisory Flash, eFUSE or External Memory. The result of the read command will be visible into the Terminal.

Note that some eFUSE bytes cannot be read for protection reasons.

Regarding the Work Flash Memory, when it is not programmed, if a reading operation occurs, an ECC error is generated. This means that Work Flash memory cannot be read when it is not programmed.

To overcome this problem, a blankcheck is performed before reading the memory via a specific API internal to the Traveo II. If the memory is blank at that specific address, then in the terminal you will see "????".

Here an example of this behaviour:

| > 02 Re | ad[0x1400FF90]: | 0x5D | 0x08 | 0xCC | 0x12 | 0x63 | 0x90 | 0x0E | 0x1E | 0x03 | 0xF4 | 0x7E | 0xA5 | 0x16 | 0xC5 | 0x5D | 0xDC |

|---------|-----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| > 02 Re | ad[0x1400FFA0]: | 0xCF | 0xCE | 0x70 | 0x44 | 0x07 | 0x8C | 0xFB | 0x35 | 0x02 | 0xDF | 0xF7 | 0x26 | 0x1A | 0x65 | 0x78 | 0x51 |

| > 02 Re | ad[0x1400FFB0]: | 0x1B | 0x26 | 0xC8 | 0x75 | 0x3D | 0x81 | 0xAB | 0xC6 | 0x0C | 0x83 | 0xC9 | 0x59 | 0xA5 | 0x14 | 0x46 | 0x8F |

| > 02 Re | ad[0x1400FFC0]: | 0x0D | 0xAD | 0xED | 0x57 | 0xA6 | 0x76 | 0x83 | 0x4D | 0xF0 | 0x01 | 0x28 | 0xFD | 0x16 | 0x13 | 0xD7 | 0xE2 |

| > 02 Re | ad[0x1400FFD0]: | 0x11 | 0x16 | 0x6A | 0xE0 | 0x3F | 0x31 | 0xBA | 0x53 | 0xD1 | 0x2A | 0xB3 | 0xEC | 0x63 | 0x7E | 0x82 | 0x00 |

| > 02 Re | ad[0x1400FFE0]: | 0xA0 | 0x5B | 0x2F | 0xFD | 0xCE | 0x70 | 0x46 | 0x26 | 0x99 | 0xAF | 0x67 | 0xCF | 0x7F | 0x7B | 0xD9 | 0xB8 |

| > 02 Re | ad[0x1400FFF0]: | 0xB1 | OxEE | 0x80 | 0x3D | 0x54 | 0x10 | 0xCE | 0x82 | 0x6B | 0x4D | 0x8B | 0xCB | 0xD3 | 0x6E | 0x94 | 0xA2 |

| > 02 Re | ad[0x14010000]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010010]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010020]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010030]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010040]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010050]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010060]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

| > 02 Re | ad[0x14010070]: | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? | ???? |

#### **#TPCMD DUMP**

**#TPCMD** DUMP <F|E|S|P|X> **#TPCMD** DUMP <F|E|S|P|X> <start address> <size> Dump command for the Main Flash, Supervisory Flash, eFUSE or External Memory.

The result of the dump command will be stored in the FlashRunner 2.0 internal memory.

As for the read command, some eFUSE bytes cannot be dumped.

The Work Flash cannot be dumped if it is not programmed because we cannot put the "????" inside a .bin file when the selected address of Work Flash memory is blank

#### **#TPCMD GET\_UNIQUE\_ID**

| Syntax:        | #TPCMD GET_UNIQUE_ID                                                                                                                   |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites: | none                                                                                                                                   |

| Description:   | This function reads the unique ID of the device<br>The result of this command will be printed on the Real Time Log and on the Terminal |

| Note:          | This command prints into Terminal and Real Time Log                                                                                    |

| Examples:      | Correct command execution: 😊                                                                                                           |

|                | #TPCMD GET_UNIQUE_ID<br>Read device unique ID:                                                                                         |

kead device unique ID: \* Unique ID0: 0x00899EB4, Unique ID1: 0xFF083D0F, Unique ID2: 0x78081C00.

#### **#TPCMD GET\_DEVICE\_INFORMATIONS**

none

Prereauisites:

Syntax:

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255

**#TPCMD** GET DEVICE INFORMATIONS

**D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

SMH

Description:

on: This function gets the device information as the family, unique ID and more

This command prints into Terminal and Real Time Log

Examples:

Note:

| #TPCMD GET DEVICE INFORMATIONS                                     |         |

|--------------------------------------------------------------------|---------|

| Read device informations:                                          |         |

| * FamilyId: 0x0104.                                                |         |

| * Revision: 0x13.                                                  |         |

| * SiliconID: 0xE6C9.                                               |         |

| * Protect state: 0x2: Virgin - [NORMAL] - Secure - Dead.           |         |

| * Life cycle stage: 0x7 - Normal Provisioned.                      |         |

| * Flash boot version: 0xA301.                                      |         |

| * SROM firmware version: 0x0601.                                   |         |

| Read device unique ID:                                             |         |

| * Unique IDO: 0x00899EB4, Unique ID1: 0xFF083D0F, Unique ID2: 0x78 | 8081C00 |

| Normal device access restrictions:                                 |         |

| * Enabled Cortex MO-AP access.                                     |         |

| * Enabled Cortex M4 AP access.                                     |         |

| * Enabled system AP access.                                        |         |

| * MPU is locked, all SRAM is accessible.                           |         |

| * Enabled Direct Execute system call functionality.                |         |

| * Entire Flash main region is accessible.                          |         |

| * Entire SRAM main region is accessible.                           |         |

| * Entire Work Flash main region is accessible.                     |         |

| * Entire Supervisory Flash main region is accessible.              |         |

| Time for Get Device Informations, 0 002 s                          |         |

## **#TPCMD OVERVIEW\_SUPERVISORY\_FLASH**

| Syntax:        | #TPCMD OVERVIEW_SUPERVISORY_FLASH                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites: | none                                                                                                                                                                          |

| Description:   | This command reads the Supervisory Flash printing its content on the Workbench Real Time Log.<br>Here below there is a little extract of the result of the command execution. |

|                | Supervisory Flash - Table of Contents Part 2 (TOC2), used to locate OEM objects:<br>Address 0x17007C00: FC010000 20122101 00000000 00000010 00000000                          |

most significant byte 0x00 then 0x00 then 0x01 and then, the less significant byte is 0xFC. If you want to reprogram this value the right data value is 0x000001FC

#### **#TPCMD OVERVIEW\_SUPERVISORY\_FLASH\_NADR**

| Syntax:        | #TPCMD OVERVIEW_SUPERVISORY_FLASH_NADR                                                                        |

|----------------|---------------------------------------------------------------------------------------------------------------|

| Prerequisites: | none                                                                                                          |

| Description:   | This command analyses the NADR (Normal/Dead Device Access Restrictions) located into the Supervisory<br>Flash |

| Examples:      | Correct command execution: 🎯                                                                                  |

VIEW\_SUPERVISORY\_FLASH\_NADF

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## **#TPCMD OVERVIEW\_SUPERVISORY\_FLASH\_SWPU**

Syntax:

#TPCMD OVERVIEW\_SUPERVISORY\_FLASH\_SWPU

Correct command execution: 😊

Prerequisites:

none

*Description:* This command analyses the SWPU, FWPU, ERPU and EWPU located into the Supervisory Flash SWPU is used to implement access restrictions to Main Flash (program/erase) and eFUSE (read/write)

Examples:

| #TPCMD OVERVIEW SUPERVISORY FLASH SWPU                         |

|----------------------------------------------------------------|

| Analyze SWPU located into Supervisory Flash:                   |

| * Found valid object size of 48 bytes.                         |

| * Get the number of FWPU (Flash Write Protection Unit) object: |

| * Found 0 FWPU object.                                         |

| * Get the number of ERPU (eFuse Read Protection Unit) object:  |

| * Found 1 ERPU object.                                         |

| * Analyze ERPU object n 1.                                     |

| * Address: 0x0000068.                                          |

| * Size: 0x80000018.                                            |

| * SL attributes: 0x00FF0007.                                   |

| * MS attributes: 0x00FF0007.                                   |

| * Get the number of EWPU (eFuse Write Protection Unit) object: |

| * Found 1 EWPU object.                                         |

| * Analyze EWPU object n 1.                                     |

| * Address: 0x0000068.                                          |

| * Size: 0x80000018.                                            |

| * SL attributes: 0x00FF0007.                                   |

| * MS attributes: 0x00FF0007.                                   |

| Value for PU OBJECT SIZE is correct.                           |

| Time for Overview Supervisory Flash SWPU: 0.003 s.             |

## **#TPCMD OVERVIEW\_SUPERVISORY\_FLASH\_TOC2**

| Syntax:        | #TPCMD OVERVIEW_SUPERVISORY_FLASH_TOC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites: | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Description:   | This command analyses the TOC2 located into the Supervisory Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Examples:      | Correct command execution: 🎯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | <pre>#TPCMD OVERVIEW_SUPERVISORY_FLASH_TOC2<br/>Analyze TOC2 located into Supervisory Flash:<br/>* Object size in bytes for CRC calculation starting from offset 0x00: 0x000001FC.<br/>* Magic number: 0x01211220.<br/>* Null-terminated table of pointers representing the SMIF configuration structure: 0x00000000.<br/>* Address of First User Application Object: 0x100000000 - Basic.<br/>* Address of Second User Application Object: 0x00000000 - Basic.<br/>* Address of Second User Application Object: 0x00000000.<br/>* Format of Second User Application Object: 0x00000000 - Basic.<br/>* Address of First CM4 or CM7 corel User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 corel User Application Object: 0x00000000.<br/>* Address of First CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Address of Second CM4 or CM7 core2 User Application Object: 0x00000000.<br/>* Number of additional objects to be verified for SECURE_HASH: 0x00000003.</pre> |

\* Address of Application Protection: 0x17007600.

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

## →smh-tech.com

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

| TOC2 Revision: 0x00000000.                                                    |

|-------------------------------------------------------------------------------|

| Controls default configuration: 0x00000242.                                   |

| * Clock frequency configuration: 50MHz, IMO + FLL (default).                  |

| * Listen window to allow sufficient time to acquire debug port: 20 ms (defau. |

|                                                                               |

- \* SWJ pins configuration: Enable SWJ pins in Flash boot (default)

- Image digital signature verification: Authentication is enabled.

Internal boothoader in flash boothoaten boothoaten is launched if other boothoaten

- onditions are met (default).

- Time for Overview Supervisory Flash TOC2: 0.003 s.

## **#TPCMD GENERATE\_HASH**

| Syntax:        | <b>#TPCMD</b> GENERATE_HASH <factory_hash all_objects></factory_hash all_objects>                                                                      |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                | FACTORY_HASH $\rightarrow$ Generates the factory hash<br>ALL_OBJECTS $\rightarrow$ Generates the hash of all objects according to TOC1 and TOC2 tables |  |

| Prerequisites: | none                                                                                                                                                   |  |

Description: This command returns the truncated SHA-256 of the Flash boot programmed in the Supervisory Flash Please refer to specific Reference Manual of your Traveo II device to have full description of how this command works

## **#TPCMD CHECK\_FACTORY\_HASH**

Syntax: **#TPCMD** CHECK FACTORY HASH

Prerequisites: none

Description: This command generates the factory hash according to TOC1 table and compares with the FACTORY1\_HASH fuses Please refer to specific Reference Manual of your Traveo II device to have full description of how this command works

## **#TPCMD COMPUTE\_BASIC\_HASH**

| Syntax:        | <b>#TPCMD</b> COMPUTE_BASIC_HASH <basic crc8sae> <start address=""> <size bytes=""></size></start></basic crc8sae>                                                                                                                                                                                                                 |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Prerequisites: | none                                                                                                                                                                                                                                                                                                                               |  |  |

| Description:   | This command generates the hash of the flash region provided as input.<br>The command allows to select between BASIC (Basic Hash) or CRC8SAE.<br>The Size Bytes parameter must be grater or equal to 1<br>Please refer to specific Reference Manual of your Traveo II device to have full description of how this<br>command works |  |  |

| Examples:      | Correct command execution: 😊                                                                                                                                                                                                                                                                                                       |  |  |

|                | Example with BASIC parameter:                                                                                                                                                                                                                                                                                                      |  |  |