02/10/2023 Driver v. 5.02 Moreno Ortolan

# Interfacing FlashRunner 2.0 with MARVELL MRV88

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# **MARVELL 88Q Introduction**

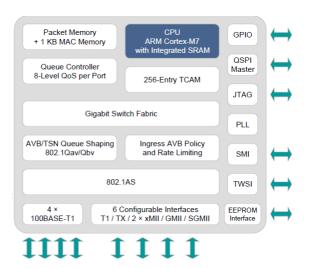

### 88Q5050:

The Marvell<sup>®</sup> 88Q5050/88Q5054 device is an AEC-Q100 qualified 8-port Ethernet switch, which is optimized for Automotive applications. Being equipped with configurable interfaces that support a combination of eight IEEE 100BASE-T1, 100BASE-TX, RGMII/RMII/MII, GMII, and SGMII ports, the switch is ideally suited for various application cases.

The switching core is designed to support all MAC ports operating at 1000 Mbps.

The 88Q5050/88Q5054 includes an ARM<sup>®</sup> CPU featured with a dedicated on-chip RAM, to support AVB protocols such as Precision Time Protocol (PTP). It provides support for TCAM with a Policy Control List (PCL) engine that supports 256 rules.

Both the low-power PHYs and the MACs integrated in the device comply fully with the applicable sections of the IEEE 802.3 standards. The IEEE 100BASE-T1 PHYs are all fully interoperable with the OPEN Alliance BroadR-Reach® (OABR) PHYs.

The 88Q5050/88Q5054 device's feature set is complemented by comprehensive local and remote management capabilities, which allow for easy access and configuration of the device.

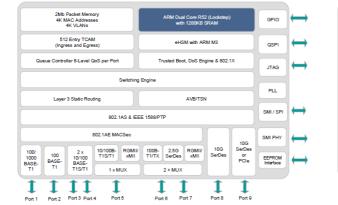

## 88Q5151, 885152, 88Q5192:

The Marvell<sup>®</sup> 88Q5152/88Q5151 is a single-chip integration of an AEC-Q100 qualified 9-Port Ethernet switch which is optimized for Automotive applications.

Being equipped with configurable interfaces that support a combination of integrated IEEE 1000BASE-T1, 10BASE-T1, 10BASE-T1S, 100BASE-TX, xMII, XFI, and PCIe ports, the switch is ideally suited for various application cases.

The switching core is designed to support all MAC ports operating at 30Gbps.

The 88Q5152/88Q5151 includes an ARM<sup>®</sup> Dual Core Lockstep R52 CPU with a dedicated on-chip RAM, to support AVB protocols such as Precision Time Protocol (PTP). It provides support for TCAM with a Policy Control List (PCL) engine that supports 512 rules. Both the low-power PHYs and the MACs integrated in the device comply fully with the applicable sections of the IEEE 802.3 standards.

The IEEE 100/1000BASE-T1 PHYs are all fully inter-operable with the OPEN Alliance BroadR-Reach® (OABR) PHYs. The feature set of the 88Q5152/88Q5151 device is complemented by comprehensive local and remote management capabilities, which allow for easy access and configuration of the device.

### 88Q5151:

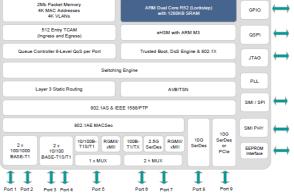

## 88Q5152:

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

## →smh-tech.com

info@smh-tech.com

SMH

# MARVELL 88Q Protocol and PIN map

880 devices support the JTAG protocol.

**#TCSETPAR** CMODE <JTAG>

# MARVELL 88Q PIN MAP

| Pin Ma   | p Tool  |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   | -    |       |

|----------|---------|-------|-------|-------|------|------------|------------|----|----|----|---------|----|-----|-------|------|---------|--------------------|-------------------------|--------------------------|-------|------------|------------|----|---|---|--------------|----------------|---|---|---|---|------|-------|

| elect y  | /our F  | lashf | Runne | er mo | del: | FR 2       | 2.0        | •  |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   | Ехро | rt to |

|          |         |       |       |       |      |            |            |    |    |    |         | l  | Mas | ter b | oard | con     | nect               | or ((                   | 2 <b>h.1</b> -           | Ch.   | B)         |            |    |   |   |              |                |   |   |   |   |      |       |

| Ţ        |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   |      | L     |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   |      |       |

| <u> </u> | 32      | 31    | 30    | 29    | 28   | <b>2</b> 7 | <b>2</b> 6 | 25 | 24 | 23 | ∎<br>22 | 21 | 20  | 19    | 18   | ∎<br>17 | 16                 | 15                      | 14                       | 13    | <b>1</b> 2 | <b>1</b> 1 | 10 | 9 | 8 | 7            | 6              | 5 | 4 | 3 | 2 | 1    |       |

| elect a  | a chai  | nnel: |       |       |      |            |            |    |    |    |         |    |     |       |      |         | Cor                | nnect                   | ion de                   | scrip | tions      | :          |    |   |   |              |                |   |   |   |   |      |       |

| • Cł     | n.1 - 8 | 38Q5  | 152 [ | [JTAG | i]   |            |            |    |    |    |         |    |     |       |      |         | DIO0: TRST Pin: A1 |                         |                          |       |            |            |    |   |   |              |                |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         | D                  | DIO1:                   | RST                      |       |            |            |    |   |   | Pin:         | B1             |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         |                    |                         |                          |       |            |            |    |   |   | <b>D</b> 2   | ~              |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         | D                  | DIO2:                   | тск                      |       |            |            |    |   |   | Pin:         |                |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         | D<br>D             | 0IO2:<br>0IO3:          | TCK<br>TDO               |       |            |            |    |   |   | Pin:         | A2             |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         | D<br>D<br>D        | 0102:<br>0103:<br>0104: | TCK<br>TDO               |       |            |            |    |   |   |              | A2<br>B2       |   |   |   |   |      |       |

|          |         |       |       |       |      |            |            |    |    |    |         |    |     |       |      |         | D<br>D<br>D<br>D   | 0102:<br>0103:<br>0104: | TCK<br>TDO<br>TDI<br>TMS |       |            |            |    |   |   | Pin:<br>Pin: | A2<br>B2<br>C2 |   |   |   |   |      |       |

# MARVELL 88Q Memory Map

| Memory Type      | Start Address | End Address | Memory Size | Page Size | Blank Value | Address Unit |

|------------------|---------------|-------------|-------------|-----------|-------------|--------------|

| [O] - OTP        | 0x00000000    | 0x0000007F  | 128 Byte    | 4         | 0x00        | BYTE         |

| [S] - SHADOW_OTP | 0x50045400    | 0x50045457  | 88 Byte     | 0         | 0x00        | BYTE         |

| Fai<br>Ma | mily: N<br>nufacturer: N | 8Q5152<br>IV88<br>IARVELL<br>IRV88 - libmrv8 | 38.50       |             |           |             |              |

|-----------|--------------------------|----------------------------------------------|-------------|-------------|-----------|-------------|--------------|

|           | Memory Type              | Start Address *                              | End Address | Memory Size | Page Size | Blank Value | Address Unit |

|           |                          | 0.0000000                                    | 0x0000007F  | 128 Byte    | 4         | 0x00        | BYTE         |

| 1         | [O] - OTP                | 0x0000000                                    | 0.00000011  |             |           |             |              |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

# UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## →smh-tech.com

# **MARVELL 88Q Driver Parameters**

The standard parameters are used to configure some specific options inside 88Q driver.

# **#TCSETPAR ENTRY\_CLOCK**

| Syntax:      | #TCSETPAR   | ENTRY         | CLOCK | <frequency></frequency> |

|--------------|-------------|---------------|-------|-------------------------|

| <i>Cyman</i> | " 100H111H( | TTL ( T T ( T | OHOOI | siroquonoy              |

Frequency> Accepted parameters 4000000, 2000000, 1000000, 500000, 100000 Hz

*Description:* Set the JTAG/SWD frequency used in the Connect procedure before raising the PLL of the device, if the device PLL is available

Note: Default value 4.00 MHz

# **#TCSETPAR SAMPLING\_POINT**

| Syntax:      | <b>#TCSETPAR</b> SAMP            | LING_POINT <value></value>                                                                                                                                                                                          |

|--------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | <value></value>                  | Accepted values are in the range 1-15                                                                                                                                                                               |

| Description: |                                  | er to permanently set the sampling point of the FPGA<br>d to leave this parameter with the default value                                                                                                            |

| Note:        | Default value 17                 |                                                                                                                                                                                                                     |

| #TCSETPAF    | R RESET_HAF                      | RDWARE [Obsolete]                                                                                                                                                                                                   |

| Syntax:      | <b>#TCSETPAR</b> RESET           | HARDWARE <value></value>                                                                                                                                                                                            |

|              | <value></value>                  | Accepted parameters YES / NO                                                                                                                                                                                        |

| Description: | Please leave this p              | et (DIO1) into Connect procedure during halt Cortex Core<br>barameter to NO except when it is strictly necessary<br>vare Reset is enough to proceed with the reset of the device and to continue with the<br>cedure |

| Note:        | This command is Default value NO | obsolete. It is available for retro compatibility only                                                                                                                                                              |

| #TCSETPAF    |                                  | UNDER_RESET [Obsolete]                                                                                                                                                                                              |

| Syntax:      | <b>#TCSETPAR</b> CONNE           | CT_UNDER_RESET <value></value>                                                                                                                                                                                      |

|              | <value> Accepted parameters YES / NO</value>                                            |

|--------------|-----------------------------------------------------------------------------------------|

| Description: | Perform a Hardware reset (DIO1) before the Connect procedure                            |

| Note:        | This command is obsolete. It is available for retro compatibility only Default value NO |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# MARVELL 88Q Driver Parameters for 88Q5050

| 88Q5050 |  |

|---------|--|

|         |  |

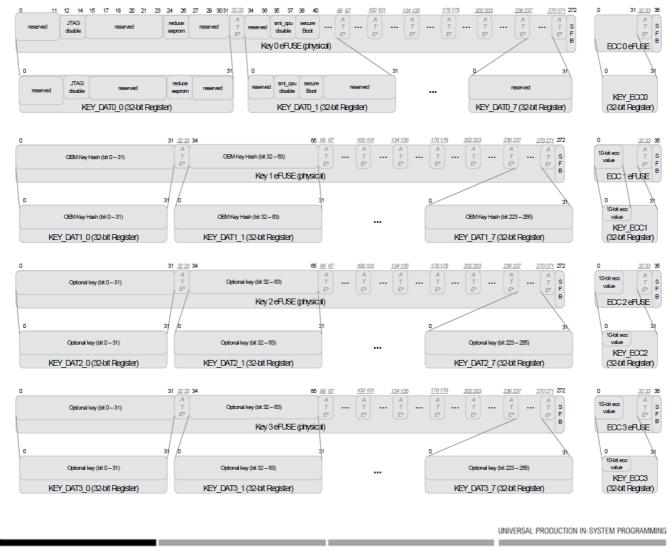

## There are eight specifics **#TCSETPAR** for **88Q5050** device:

| <b>#TCSETPAR</b> KEY_DAT0 [255] - [223] - [191] - [159] - [127] - [95] - [63] - [31] - [0] - KEY_SFB_DAT0 |

|-----------------------------------------------------------------------------------------------------------|

| <b>#TCSETPAR</b> KEY_ECC0 - KEY_SFB_ECC0                                                                  |

| <b>#TCSETPAR</b> KEY_DAT1 [255] - [223] - [191] - [159] - [127] - [95] - [63] - [31] - [0] - KEY_SFB_DAT1 |

| <b>#TCSETPAR</b> KEY_ECC1 KEY_ECC1 - KEY_SFB_ECC1                                                         |

| <b>#TCSETPAR</b> KEY_DAT2 [255] - [223] - [191] - [159] - [127] - [95] - [63] - [31] - [0] - KEY_SFB_DAT2 |

| <b>#TCSETPAR</b> KEY_ECC2 KEY_ECC2 - KEY_SFB_ECC2                                                         |

| <b>#TCSETPAR</b> KEY_DAT3 [255] - [223] - [191] - [159] - [127] - [95] - [63] - [31] - [0] - KEY_SFB_DAT3 |

| <b>#TCSETPAR</b> KEY_ECC3 KEY_ECC3 - KEY_SFB_ECC3                                                         |

These parameters are used to write the corresponding fuse.

If the bit KEY\_SFB\_DAT 0/1/2/3 or KEY\_SFB\_ECC 0/1/2/3 is set to 1, then it will be impossible to rewrite the corresponding eFUSE.

The internal procedure always programs these registers starting from the third up to the zero. This is because, if we did the reverse procedure, there could be the possibility that by programming the KEY\_DAT0 register the JTAG will be disabled forever.

In the driver's internal procedure, we must specify some choices made to handle various cases that could occur:

1. If user not set any **#TCSETPAR** but set **#TPCMD** PROGRAM E and/or **#TPCMD** VERIFY E R, there are no data to write into device, so the program/verify procedure is skipped and there's a warning into LOG like this:

Nothing to program. Skipping eFuses programming procedure

2. If a **#TCSETPAR** of an eFUSE is set and the user tries to program this eFUSE with the **#TPCMD** PROGRAM E procedure, but the corresponding KEY\_SFB\_DAT 0/1/2/3 or KEY\_SFB\_ECC 0/1/2/3 is already set to 1, it's impossible to write this eFUSE.

To manage this situation, the programming procedure of this eFuses is skipped and the PROGRAM E procedure continue normally.

There's a warning into LOG like this:

Warning: KEY\_SFB\_DAT 0/1/2/3 or KEY\_SFB\_ECC 0/1/2/3 is already set to 1 KEY DAT 0/1/2/3 or KEY ECC 0/1/2/3 eFUSE is not writable anymore.

3. If the bits that disable the JTAG are set to 1 in KEY\_DAT0, there is a special procedure for programming this eFUSE.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

We need to do a special procedure because if we program the eFUSE directly with these bits, the JTAG is immediately disabled and it's impossible to continue communicating with the device.

So, in this case, in the program procedure there's this warning into LOG:

#### Skipped jtag disable bits. These bits are written only at the end of procedure if all is ok. Is impossible to write these bits now. We need to maintain the itag active for communication

And if the KEY\_SFB\_DAT 0 bit is set to 1 there's another warning into LOG:

EY\_SFB\_DATO bit is set to 1. We need to complete the eFuse procedure at the end of program.

So, at this point, into **#TPCMD** PROGRAM E procedure, we program the entire eFUSEs without the JTAG disable bits and with KEY\_SFB\_DAT0 set to 0.

After that, if all is ok, so **#TPCMD PROGRAM** E response with "PASS" and the subsequent commands respond with a "PASS", in the **#TPCMD DISCONNECT** command we program the JTAG disable bits and KEY\_SFB\_DAT0 if it's set to 1.

If the Jtag disable bits are set into KEY DAT0 eFuse, the JTAG is disabled immediately, it's impossible to read/write a register inside 88Q5050 device.

Into LOG you can see this message:

Disable JTAG now.

At this point we need to close the communication because JTAG cannot longer be used.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

# **MARVELL 88Q Driver Commands**

Here you can find the complete list of all available commands for 88Q driver.

E → eFUSE O → OTP area S → Shadow OTP area

# **#TPCMD CONNECT**

### **#TPCMD** CONNECT

This function performs the entry and is the first command to be executed when starting the communication with the device.

### 88Q5050:

```

---#TPCMD CONNECT

Protocol selected JTAG.

Entry Clock is 4.00 MHz.

Trying Hot Plug connect procedure.

ID-Code read correctly at 4.00 MHz.

JTAG-SWD Debug Port enabled.

Scanning AP map to find all APS.

AP[0] IDR: 0x74770001, Type: AMBA AHB3 bus

AP[0] ROM table base address 0xE00FD000.

CPUID: 0x411FC271.

Implementer Code: 0x41 - [ARM].

Found Cortex M7 revision r1p1.

Cortex M7 Core halted [0.102 s].

Requested Clock is 25.00 MHz.

Generated Clock is 25.00 MHz.

Good samples: 5 [Range 3 ~ 7]

ID-Code read correctly at 25.00 MHz.

Time for Connect: 0.207 s.

```

### 88Q5151:

```

---#TPCMD CONNECT

Protocol selected JTAG.

Entry Clock is 4.00 MHz.

Trying Hot Plug connect procedure.

ID-Code read correctly at 4.00 MHz.

JTAG-SWD Debug Port enabled.

Cortex R52 Core halted [0.002 s].

Requested Clock is 37.50 MHz.

Generated Clock is 37.50 MHz.

Good samples: 3 [Range 4 ~ 6]

ID-Code read correctly at 37.50 MHz.

Time for Connect: 0.106 s.

```

# **#TPCMD BLANKCHECK**

### **#TPCMD** BLANKCHECK <E>

Blankcheck available only for eFUSE memory of 88Q5050 device. Verify if all memory is erased.

# **#TPCMD PROGRAM**

### **#TPCMD** PROGRAM <E>

Program available only for eFUSE memory of 88Q5050 device. Programs all memory of the selected type based on the data in the FRB file.

### **#TPCMD** PROGRAM <0>

Program available only for OTP memory of 88Q51x devices. Programs all memory of the selected type based on the data in the FRB file.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## →smh-tech.com

### **#TPCMD** PROGRAM <0> <start address> <size>

Program available only for OTP memory of 88Q51x devices. Programs selected part of memory of the selected type based on the data in the FRB file. Enter the Start Address and Size in hexadecimal format.

# **#TPCMD VERIFY**

## **#TPCMD** VERIFY <E> <R>

R: Readout Mode. Verify Readout available only for eFUSE memory of 8805050 device. Verify all memory of the selected type based on the data in the FRB file.

## **#TPCMD** VERIFY <0> <R>

R: Readout Mode. Verify Readout available only for OTP memory of 88Q51x devices. Verify all memory of the selected type based on the data in the FRB file.

## **#TPCMD** VERIFY <0> <R> <start address> <size>

#### R: Readout Mode.

Verify Readout available only for OTP memory of 88Q51x devices. Verify selected part of memory of the selected type based on the data in the FRB file. Enter the Start Address and Size in hexadecimal format.

# **#TPCMD READ**

#### **#TPCMD** READ <E>

Read command available only for eFUSE memory of 88Q5050 device. The result of the read command will be visible into the Terminal.

## **#TPCMD** READ <0|S>

**#TPCMD** READ <0|S> <start address> <size> Read command available for OTP and Shadow OTP memory of 88Q51x devices. The result of the read command will be visible into the Terminal.

# **#TPCMD DUMP**

```

#TPCMD DUMP <0|S>

```

**#TPCMD** DUMP <0|S> <start address> <size> Dump command available for OTP and Shadow OTP memory of 88Q51x devices.

The result of the dump command will be stored in the FlashRunner 2.0 internal memory.

# **#TPCMD INFO**

| Syntax:        | #TPCMD INFO                                                |

|----------------|------------------------------------------------------------|

| Prerequisites: | This command can be executed without <b>#TPCMD</b> CONNECT |

| Description:   | Print driver informations for 88Q5050 device               |

| Note:          | This command prints into Real Time Log                     |

Correct command execution: 😊

Examples:

---#TPCMD INFO For KEY 0/1/2/3 eFuses are expected eleven parameters. The first eight parameters are KEY\_DAT 0/1/2/3. The order of KEY\_DAT 0/1/2/3 parameters are: [255] [223] [191] [159] [127] [95] [63] [31] [0] The ninth parameter is KEY\_SFB\_DAT 0/1/2/3.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## →smh-tech.com

For KEY\_ECC 0/1/2/3 eFuses are expected two parameter The first parameter is KEY\_ECC 0/1/2/3. The second parameter is KEY\_SFB\_ECC 0/1/2/3. Time for eFuse Info: 0.001 s

# **#TPCMD READ\_MEM8**

| #TPCMD R        | EAD_MEM8                                                                                                                                                                                                                            |                                                                                                                |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:         | <b>#TPCMD</b> READ_MEM8 <add< td=""><td>ress&gt; <byte count=""></byte></td></add<>                                                                                                                                                 | ress> <byte count=""></byte>                                                                                   |  |  |  |  |

|                 | <address><br/><byte count=""></byte></address>                                                                                                                                                                                      | Address in HEX format (i.e., 0x52002020)<br>Byte count in decimal format (i.e., 8 -> eight bytes)              |  |  |  |  |

| Prerequisites:  | none                                                                                                                                                                                                                                |                                                                                                                |  |  |  |  |

| Description:    | Read memory byte per by                                                                                                                                                                                                             | rte from target 88Q device                                                                                     |  |  |  |  |

| Note:           |                                                                                                                                                                                                                                     | e from driver version <b>4.06</b><br>Terminal and Real Time Log                                                |  |  |  |  |

| Examples:       | Correct command executi                                                                                                                                                                                                             | ion: 😊                                                                                                         |  |  |  |  |

|                 | #TPCMD READ_MEM8 0x<br>Read[0x52002020]: 0xF0<br>Read[0x52002021]: 0xAA<br>Read[0x52002022]: 0x10<br>Read[0x52002023]: 0x14<br>Read[0x52002024]: 0x00<br>Read[0x52002025]: 0x00<br>Read[0x52002027]: 0x00<br>Time for Read Mem: 0.0 |                                                                                                                |  |  |  |  |

| <b>#TPCMD</b> R | EAD_MEM16                                                                                                                                                                                                                           |                                                                                                                |  |  |  |  |

| Syntax:         | <b>#TPCMD</b> READ_MEM16 <ad< td=""><td>dress&gt; &lt;16-bit Word Count&gt;</td></ad<>                                                                                                                                              | dress> <16-bit Word Count>                                                                                     |  |  |  |  |

|                 | <address><br/>&lt;16-bit Word Count&gt;</address>                                                                                                                                                                                   | Address in HEX format (i.e., 0x52002020)<br>16-bit Word count in decimal format (i.e., 4 -> four 16-bit words) |  |  |  |  |

| Prerequisites:  | none                                                                                                                                                                                                                                |                                                                                                                |  |  |  |  |

| Description:    | Read memory 16-bit word                                                                                                                                                                                                             | l per 16-bit word from target 88Ω device                                                                       |  |  |  |  |

| Note:           | This command is available from driver version <b>4.06</b><br>This command prints into Terminal and Real Time Log                                                                                                                    |                                                                                                                |  |  |  |  |

| Examples:       | Correct command executi                                                                                                                                                                                                             | ion: 🌝                                                                                                         |  |  |  |  |

|                 | #TPCMD READ_MEM16 0<br>Read[0x52002020]: 0xAP<br>Read[0x52002022]: 0x14<br>Read[0x52002024]: 0x00<br>Read[0x52002026]: 0x00<br>Time for Read Mem: 0.0                                                                               | NF0<br>116<br>000<br>000                                                                                       |  |  |  |  |

| <b>#TPCMD</b> R | EAD_MEM32                                                                                                                                                                                                                           |                                                                                                                |  |  |  |  |

| Syntax:         | <b>#TPCMD</b> READ_MEM32 <ad< td=""><td>dress&gt; &lt;32-bit Word Count&gt;</td></ad<>                                                                                                                                              | dress> <32-bit Word Count>                                                                                     |  |  |  |  |

|                 | <address><br/>&lt;32-bit Word Count&gt;</address>                                                                                                                                                                                   | Address in HEX format (i.e., 0x52002020)<br>32-bit Word count in decimal format (i.e., 2 -> two 32-bit words)  |  |  |  |  |

| Prerequisites:  | none                                                                                                                                                                                                                                |                                                                                                                |  |  |  |  |

|                 |                                                                                                                                                                                                                                     | UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING                                                                     |  |  |  |  |

SMH Technologies S.r.l.

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S\* 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

Description:

Read memory 32-bit word per 32-bit word from target 88Q device This command is available from driver version 4.06

This command prints into Terminal and Real Time Log

Examples:

Note:

Correct command execution: 😊

READ\_MEM32 ---#TPCMD READ\_MEM32 0x52002020 2 Read[0x52002020]: 0x1416AAF0 Read[0x52002024]: 0x00000000 Read Mem:

# **#TPCMD DISCONNECT**

**#TPCMD** DISCONNECT

Disconnect function. Power off and exit.

**HQ and Registered Office** Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 **REA** PN-97255

D-U-N-S® 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

## →smh-tech.com

# MARVELL 88Q Driver Changelog

Info about driver version 1.00 - 22/11/2019 Supported 88Q5050 device.

**Info about driver version 1.01 - 04/01/2020** Fixed verify readout procedure.

**Info about driver version 2.00 - 03/02/2020** Supported FPGA static 9.

Info about driver version 2.01 - 19/03/2020 Fixed small printout bug of address value into Read command.

Info about driver version 2.02 - 27/03/2020 Now Connect command is able to detect if JTAG fuse are burned.

**Info about driver version 4.00 - 14/12/2020** Added new JTAG Fpga to support FlashRunner HS. Added PLL, Sampling Point and DMA management.

Info about driver version 4.01 - 06/04/2021 Added new JTAG Fpga for FlashRunner HS GP2 and GP4.

**Info about driver version 4.02 - 19/07/2021** Internal update for FPGA name and version tracking.

Info about driver version 4.03 - 12/08/2021 Internal upgrade of the algorithm, no change to the operations it performs.

**Info about driver version 4.04 - 25/08/2021** Driver name changed from libmrv\_88.so to libmrv88.so. Internal upgrade of the algorithm, no change to the operations it performs.

Info about driver version 4.05 - 04/11/2021 Internal update, upgraded management for JTAG FPGA reset.

Info about driver version 4.06 - 25/01/2022 Added READ\_MEM8, READ\_MEM16, READ\_MEM32 commands.

**Info about driver version 4.07 - 16/06/2022** Print current FPGA version loaded into TPSTART command. Upgraded internal code to align all drivers.

Info about driver version 5.00 - 31/07/2022 Added FPGA for new FlashRunner 2.0 models.

**Info about driver version 5.01 - 16/06/2023** Supported 88Q51x series.

Info about driver version 5.02 – 02/10/2023 Internal driver update.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING