14/03/2025 Driver v. 5.14 Moreno Ortolan

# Interfacing FlashRunner 2.0 with NXP KINETIS

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# **NXP KINETIS Families**

# KINETIS K32 L Series Arm Cortex M4/M0+

#### K32 L Series: Ultra-Low Power Microcontrollers (MCUs) Optimized for Low-Leakage Applications

Based on the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 and Cortex-M0+ architectures, K32 L series MCUs provide software and tool enablement via MCUXpresso suite of tools, and scalability making this portfolio an ideal fit for IoT applications. The K32 L series of MCUs is part of NXP's EdgeVerse<sup>™</sup> edge computing platform.

|                                              | CPU                             |                                 | Packages                     |           | Cor | nms | НМІ | Sec | curity |

|----------------------------------------------|---------------------------------|---------------------------------|------------------------------|-----------|-----|-----|-----|-----|--------|

| Family                                       | Arm Cortex-M                    | Memory                          |                              | Pin Count |     |     |     |     |        |

| K32 L3<br>Energy Efficient and Secure        | Cortex-M4 and Cortex-M0+ 72 MHz | Up to 1.25 MB Flash 384 kB SRAM | VFBGA, MBGA, LQFP, QFN, LQFP | 64-176    | ~   | ~   | ~   | ~   | ~      |

| K32 L2<br>Ultra-Low-Power, Highly Integrated | Cortex-M0+ 72 MHz               | 64-512 kB Flash, 32-128 kB RAM  | QFN, LQFP, MAPBGA            | 32-100    | -   | ~   | ~   | ~   | -      |

# **KINETIS K Series Arm Cortex M4**

Kinetis® K Series: High-Performance Microcontrollers (MCUs) Based on Arm® Cortex®-M4 Core

Kinetis K series MCUs offer optimized performance, scalable integration and low-power capabilities.

|                            | CPU           |                                                 |                             |   | Comm | S | Ŀ | MI |   | Security | V |

|----------------------------|---------------|-------------------------------------------------|-----------------------------|---|------|---|---|----|---|----------|---|

| Sub-Families               | Arm Cortex-M4 | Memory                                          | Packages                    |   |      |   |   |    |   |          |   |

| K8x<br>Scalable and Secure | 150 MHz       | 256 KB Flash<br>256 KB SRAM, XIP QuadSPI        | LQFP, MAPBGA,<br>WLCSP      | - | -    | ~ | - |    | ~ | ~        | ~ |

| K7x<br>Graphic LCD         | 120–150 MHz   | 1 MB Flash<br>128 KB SRAM                       | MAPBGA                      | ~ | ~    | ~ | ~ | -  | ~ | ~        | - |

| K6x<br>Ethernet            | 100–180 MHz   | 256 KB–2 MB Flash<br>64–256 KB SRAM             | LQFP, MAPBGA,<br>WLCSP      | ~ | ~    | ~ | - | -  | ~ | ~        | - |

| K5x<br>Measurement         | 72–100 MHz    | 160–512 KB Flash<br>32–128 KB SRAM              | LQFP, MAPBGA                | ~ | -    | ~ | - | ~  | ~ | -        | - |

| K4x<br>USB and segment LCD | 72–100 MHz    | 64–512 KB Flash<br>16–128 KB SRAM               | LQFP, MAPBGA                | - | ~    | ~ | - | ~  | - | -        | - |

| K3x<br>Segment LCD         | 72–100 MHz    | 64–512 KB Flash<br>16–128 KB SRAM               | LQFP, MAPBGA                | - | ~    | - | - | ~  | - | -        | - |

| K2x / KS2x<br>USB          | 50–180 MHz    | 32 KB–2 MB Flash<br>8 KB–1 MB SRAM, XIP QuadSPI | LQFP, QFN,<br>MAPBGA, WLCSP | - | ~    | ~ | - | -  | ~ | ~        | - |

| <b>K1x</b><br>Mainstream   | 50–120 MHz    | 32 KB–1 MB Flash<br>8–128 KB SRAM               | LQFP, QFN,<br>MAPBGA        | - | ~    | - | - | -  | ~ | ~        | - |

| K0x<br>Entry-level         | 100 MHz       | 64–128 KB Flash<br>16 KB SRAM                   | LQFP,<br>QFN                | - | -    | - | - | -  | - | -        | - |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021

# UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# KINETIS KL Series Arm Cortex M0+

#### Kinetis® L Series: Ultra-Low Power Microcontrollers (MCUs) Based on Arm® Cortex®-M0+ Core

Kinetis<sup>®</sup> L series MCU portfolio includes more than 200 compatible, low-power, high-performance 32-bit MCUs. This series combines the low-power performance and energy-efficiency of the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ core with the peripheral sets, enablement and scalability of the Kinetis MCU portfolio of solutions for internet of things (IoT) applications.

|                             | CPU                          |                                       | Packages                              |           | Cor | nms | н | МІ | Sec | urity            |

|-----------------------------|------------------------------|---------------------------------------|---------------------------------------|-----------|-----|-----|---|----|-----|------------------|

| Products                    | Arm<br>Cortex-M0+            | Memory                                |                                       | Pin Count |     |     |   |    |     | Tamper Detection |

| KL8x<br>Security            | 72 MHz<br>(Up to 96 MHz)     | 128 KB Flash<br>96 KB SRAM            | LQFP, MAPBGA,<br>WLCSP                | 64 – 121  | ~   | ~   | ~ | ~  | ~   | ~                |

| KL4x<br>USB and Segment LCD | 48 MHz                       | 128 – 256 KB Flash<br>16 – 32 KB SRAM | LQFP, MAPBGA                          | 64 – 121  | ~   | ~   | ~ | ~  | -   | -                |

| KL3x<br>Segment LCD         | 48 MHz                       | 32 – 256 KB Flash<br>4 – 32 KB SRAM   | LQFP, MAPBGA                          | 64 – 121  | ~   | -   | ~ | ~  | -   | -                |

| KL2x<br>USB                 | 48 MHz / 72MHz<br>(Up to 96) | 32 – 512 KB Flash<br>4 – 128 KB SRAM  | LQFP, QFN,<br>MAPBGA, XFBGA,<br>WLCSP | 32 - 121  | ~   | ~   | ~ | -  | ~   | -                |

| KL1x<br>Mainstream          | 48 MHz                       | 32 – 256 KB Flash<br>4 – 32 KB SRAM   | LQFP, QFN,<br>MAPBGA, XFBGA,<br>WLCSP | 32 - 80   | ~   | -   | ~ | -  | -   | -                |

| KL0x<br>Entry-Level         | 48 MHz                       | 8 – 32 KB Flash<br>1 – 4 KB SRAM      | LQFP, QFN<br>WLCSP                    | 16 – 48   | -   | -   | - | -  | -   | -                |

# KINETIS KV Series Arm Cortex M4/M0+/M7

#### KV Series: Real-Time Motor Control and Power Conversion MCUs Based on Arm® Cortex®-M0+/M4/M7

KV Series of MCUs are part of the EdgeVerse<sup>™</sup> edge computing platform and are designed to support a wide range of BLDC, PMSM and ACIM motor control as well as digital power conversion applications.

|                                  | СРИ                        | Memory                          |                 |                    |          | Timer | s |   |                     | Anal                     | og |   | Conne | ectivity | Sec | urity |

|----------------------------------|----------------------------|---------------------------------|-----------------|--------------------|----------|-------|---|---|---------------------|--------------------------|----|---|-------|----------|-----|-------|

| Products                         |                            | Flash /<br>SRAM                 | Packages        |                    |          |       |   |   |                     |                          |    |   |       |          |     |       |

| KV5x<br>Power Conversion         | Cortex-M7<br>240 MHz       | 512 KB – 1 MB /<br>128 – 256 KB | lqfp,<br>Mapbga | 2 x 8ch<br>2 x 2ch | 2 x 12ch | ~     | ~ | ~ | 1 x 12ch<br>(260pS) | 4 x 12bit<br>(5 Msps)    | ~  | ~ | ~     | ~        | ~   | ~     |

| KV4x<br>High Performance Motor   | Cortex-M4<br>168 MHz       | 64 – 256 KB /<br>16 – 32 KB     | LQFP            | 2 x 8ch<br>1 x 2ch | 1 x 12ch | ~     | ~ | ~ | 1 x 12ch<br>(312pS) | 2 x 12bit<br>(4.1 Msps)  | ~  | ~ | -     | ~        | ~   | -     |

| KV3x<br>Sensorless Motor Control | Cortex-M4<br>100 – 120 MHz | 64 – 512 KB /<br>16 – 96 KB     | LQFP,<br>QFN    | 2 x 8ch<br>2 x 2ch | -        | ~     | ~ | - | -                   | 2 x 16-bit<br>(1.2 Msps) | ~  | ~ | -     | -        | ~   | -     |

| KV1x<br>Entry-Level              | Cortex-M0+<br>75 MHz       | 16 – 128 KB /<br>8 – 16 KB      | LQFP,<br>QFN    | 2 x 6ch<br>2 x 2ch | -        | ~     | ~ | - | -                   | 2 x 16-bit<br>(1.2 Msps) | ~  | ~ | -     | ~        | ~   | -     |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S\* 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021

# UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# KINETIS KE Series Arm Cortex M4/M0+

#### Kinetis® E Series: 5V, Robust Microcontrollers (MCUs) Based on Arm® Cortex®-M0+/M4 Core

The 5V KE series of MCUs are part of the EdgeVerse<sup>™</sup> edge computing platform and are designed to maintain high-reliability and robustness in harsh electrical noise environments, targeting white goods and industrial applications.

|                                        | СРИ                         |                                       |                                                                          |         | Com     | munication Inter | faces                |                |

|----------------------------------------|-----------------------------|---------------------------------------|--------------------------------------------------------------------------|---------|---------|------------------|----------------------|----------------|

| Products                               |                             | Memory                                | Packages                                                                 |         | SPI     | LPUART           | CAN                  | TSI            |

| KE1xF<br>Performance w/<br>CAN         | 168 MHz<br>Cortex-M4 w/ FPU | 256 – 512 KB Flash<br>32 – 64 KB SRAM | 64-LQFP, 100-LQFP                                                        | 2       | 2       | 3                | up to 2 x<br>FlexCAN | -              |

| KE1xZ<br>Mainstream w/<br>Touch        | 72 MHz<br>Cortex®-M0+       | 32 – 256 KB Flash<br>4 – 32 KB SRAM   | 44-LQFP, 48-LQFP,<br>64-LQFP, 100-LQFP,<br>40-QFN                        | 2       | 2       | 3                | 1                    | Up to<br>50 ch |

| KE06<br>Entry-Level w/<br>CAN          | 48 MHz<br>Cortex®-M0+       | 64 – 128 KB Flash<br>8 – 16 KB SRAM   | 44-LQFP, 64-LQFP,<br>64-QFP,80-LQFP                                      | 2       | 2       | 3                | 1                    | -              |

| KE04<br>Entry-Level w/<br>Mixed Signal | 48 MHz<br>Cortex®-M0+       | 8 – 128 KB Flash<br>1 – 16 KB SRAM    | 16-TSSOP, 24-QFN,<br>44-LQFP, 64-LQFP,<br>64-QFP, 80-LQFP,<br>20-SOIC WB | Up to 2 | Up to 2 | Up to 3          | -                    | -              |

| KE02<br>Entry-Level w/<br>EEPROM       | 20 - 40 MHz<br>Cortex®-M0+  | 16 – 64 KB Flash<br>2 – 4 KB SRAM     | 32-QFN, 32-LQFP,<br>44-LQFP, 64-LQFP,<br>64-QFP                          | 1       | 2       | Up to 3          | -                    | -              |

## **KINETIS KM Series Arm Cortex M0+**

#### KM Series: Metrology Microcontrollers (MCUs) Based on Arm® Cortex®-M0+ Core

KM series low-power MCUs are part of the EdgeVerse<sup>™</sup> edge computing platform and are designed to support single-chip designs for one-, two- and three-phase electricity meters, flow meters and other precision measurement applications.

|                         | СРИ               | Memory                      |                                | Development<br>Hardware                          | нмі             | Co                           | mms |         |   | Sec | curity   |

|-------------------------|-------------------|-----------------------------|--------------------------------|--------------------------------------------------|-----------------|------------------------------|-----|---------|---|-----|----------|

| Products                | Arm<br>Cortex-M0+ | Flash /<br>SRAM             | Packages                       | Tower Module                                     | SLCD            | UART<br>(ISO7816/<br>LPUART) |     |         |   |     |          |

| <b>KM1x</b><br>Baseline | 50 MHz            | 64 – 128 KB /<br>16 KB      | 44LGA                          | TWR-KM34Z50M(V3)                                 | N/A             | 2<br>(2 / -)                 | 1   | 2       | ~ | ~   | N/A      |

| KM3x<br>Segment LCD     | 50–75 MHz         | 64 – 512 KB /<br>16 – 64 KB | 64LQFP,<br>100LQFP,<br>144LQFP | TWR-KM34Z50M(V3)<br>TWR-KM34Z75M<br>TWR-KM35Z75M | Up to<br>56 X 8 | 4-5<br>(2 / 0-1)             | 2   | Up to 3 | ~ | ~   | Optional |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# KINETIS KW Series Arm Cortex M33/M0+

#### KW Series: Bluetooth<sup>®</sup> Smart/Bluetooth Low Energy

Our Bluetooth Smart (Bluetooth Low Energy) solutions include highly integrated SoCs with plentiful Flash and SRAM memory utilizing Arm® Cortex®-M cores. These products enable ultra-low-power operation without compromising radio performance. In addition to providing complete SoCs, a host Bluetooth Low Energy stack is provided, as well as several GATT profiles and services.

|                                                                                                                          |                | Memory                    |                             | Supported<br>Protocols  |                                                  | Radio Perfo       | ormance            |                     |

|--------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------|-----------------------------|-------------------------|--------------------------------------------------|-------------------|--------------------|---------------------|

| Product                                                                                                                  | СРИ            | Flash /<br>SRAM           | Supported<br>Frequency Band | Bluetooth Low<br>Energy |                                                  | Transmit<br>Power | Receive<br>Current | Transmit<br>Current |

| KW45<br>Bluetooth 5.3 Long-Range MCUs with CAN FD and LIN<br>Bus Options, Arm <sup>®</sup> Cortex <sup>®</sup> -M33 Core | Cortex-<br>M33 | KW45: Up to<br>1MB/128 kB | 2.4 GHz                     | 5.3                     | 97.5 dBm (1<br>Mbit/s)<br>-106 dBm (125<br>Kbps) | -25 to<br>+10 dBm | 4.7 mA             | 4.6 mA @ 0<br>dBm   |

|                                                                                                                                |                | Memory                                                     |                             | Supported<br>Protocols  | I                                               | Radio Perform      |                    |                     |

|--------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|-----------------------------|-------------------------|-------------------------------------------------|--------------------|--------------------|---------------------|

| Product                                                                                                                        | CPU            | Flash /<br>SRAM                                            | Supported<br>Frequency Band | Bluetooth Low<br>Energy | Sensitivity                                     | Transmit<br>Power  | Receive<br>Current | Transmit<br>Current |

| KW39/38/37<br>Bluetooth 5.0 Long-Range MCUs with CAN FD and LIN<br>Bus Options, Arm <sup>®</sup> Cortex <sup>®</sup> -M0+ Core | Cortex-<br>M0+ | KW37: 512 KB/64 kB<br>KW38/39: 512 KB/64<br>kB+8 kB EEPROM | 2.4 GHz                     | 5.0                     | -98 dBm (1<br>Mbit/s)<br>-105 dBm (125<br>Kbps) | -25 to<br>+5 dBm   | 6.8 mA             | 6.1 mA              |

| KW36/35/34<br>Automotive Qualified Bluetooth 5 MCUs and General<br>FSK                                                         | Cortex-<br>M0+ | KW35: 512 KB/64 kB;<br>KW36: 512 KB/64 kB+8<br>kB EEPROM   | 2.4 GHz                     | 5.0                     | -95 dBm                                         | -25 to<br>+3.5 dBm | 6.8 mA             | 6.1 mA              |

| KW31Z<br>Bluetooth Low Energy 4.2                                                                                              | Cortex-<br>M0+ | 256-512 kB /<br>64-128 kB                                  | 2.4 GHz                     | 4.2                     | -95 dBm<br>(Bluetooth Low<br>Energy)            | Up to<br>+3.5 dBm  | 6.8 mA             | 6.1 mA              |

# **KINETIS KEA Series Arm Cortex M0+**

#### Ultra-Reliable KEA Automotive Microcontrollers (MCUs) based on Arm® Cortex®-M0+ Core

Kinetis<sup>®</sup> EA series of 32-bit Arm<sup>®</sup> Cortex<sup>®</sup> MCUs are targeted for a wide range of automotive and industrial applications requiring the highest level of quality and longevity support.

The Kinetis EA series is an entry point to the broad Arm ecosystem and features:

- A low-power Arm Cortex-M0+ core and 8–128 KB of embedded flash

- Excellent EMC/ESD, high temperature, and low radiated emissions

- Scalable, highly robust performance solution for cost-sensitive automotive applications

- A broad set of reference designs, tools and application notes to help shorten design development and speed time-tomarket

| Device  | Flash | RAM | EEPROM   | Freq  | MSCAN | SCI | SPI | ATD    | Flex-Tim     | IIC | GPIO     | Packages        |

|---------|-------|-----|----------|-------|-------|-----|-----|--------|--------------|-----|----------|-----------------|

| KEAZN8  | 8K    | 1K  | Emulated | 48MHz | 0     | 1   | 1   | 12c12b | 6c+2c 16b    | 1   | Up to 22 | 16 TSSOP/24 QFN |

| KEAZN16 | 16K   | 2К  | 256B     | 40MHz | 0     | 3   | 2   | 16c12b | 6c+2c+2c 16b | 2   | Up to 57 | 32/64 LQFP      |

| KEAZN32 | 32K   | 4K  | 256B     | 40MHz | 0     | 3   | 2   | 16c12b | 6c+2c+2c 16b | 2   | Up to 57 | 32/64 LQFP      |

| KEAZN64 | 64K   | 4K  | 256B     | 40MHz | 0     | 3   | 2   | 16c12b | 6c+2c+2c 16b | 2   | Up to 57 | 32/64 LQFP      |

| KEAZ64  | 64K   | 8K  | Emulated | 48MHz | 1     | 3   | 2   | 16c12b | 6c+2c+2c 16b | 2   | Up to 71 | 64/80 LQFP      |

| KEAZ128 | 128K  | 16K | Emulated | 48MHz | 1     | 3   | 2   | 16c12b | 6c+2c+2c 16b | 2   | Up to 71 | 64/80 LQFP      |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

# **NXP KINETIS Protocol and PIN map**

KINETIS devices support the SWD protocol.

**#TCSETPAR** CMODE <SWD>

# **NXP KINETIS PIN MAP**

| 🔋 Pin Ma | ap Tool |       |      |       |       |     |       |      |      |    |    |    |     |       |      |       |             |       |                |            |        |    |    |   |   |                                      |              |    |   |   |   | _    |        | ×   |

|----------|---------|-------|------|-------|-------|-----|-------|------|------|----|----|----|-----|-------|------|-------|-------------|-------|----------------|------------|--------|----|----|---|---|--------------------------------------|--------------|----|---|---|---|------|--------|-----|

| Select   |         |       | Runn | er me | odel: | FR  | 2.0   |      |      |    |    |    |     |       |      |       |             |       |                |            |        |    |    |   |   |                                      |              |    |   |   |   | Expo | ort to | PDF |

|          |         |       |      |       |       |     |       |      |      |    |    |    | Mas | ter b | oarc | l con | inect       | tor ( | Ch.1           | - Ch       | .8)    |    |    |   |   |                                      |              |    |   |   |   |      |        |     |

| ļ        |         |       |      |       |       |     |       |      |      |    |    |    |     |       |      |       |             |       |                |            |        |    |    |   |   |                                      |              |    |   |   |   |      | l      | с   |

|          |         |       |      |       |       |     |       |      |      |    |    |    |     |       |      |       |             |       |                |            |        |    |    |   |   |                                      |              |    |   |   |   |      |        | в   |

|          |         |       |      |       |       |     |       |      |      |    |    |    |     |       |      |       |             |       |                |            |        |    |    |   |   |                                      |              |    |   |   |   |      |        | A   |

|          | 32      | 31    | 30   | 29    | 28    | 27  | 26    | 25   | 24   | 23 | 22 | 21 | 20  | 19    | 18   | 17    | 16          | 15    | 14             | <b>1</b> 3 | 12     | 11 | 10 | 9 | 8 | 7                                    | 6            | 5  | 4 | 3 | 2 | 1    |        |     |

| Select   | a cha   | nnel: |      |       |       |     |       |      |      |    |    |    |     |       |      |       | Co          | Innec | tion de        | escrij     | ptions | s: |    |   |   |                                      |              |    |   |   |   |      |        |     |

| • C      | h.1 - ľ | MKE1  | 7Z25 | 6xxx  | 7_1x  | _МХ | 25L64 | 433F | [SWI | D] |    |    |     |       |      |       | D<br>D<br>V |       | : SWC<br>: SWD | CLK        |        |    |    |   |   | Pin:<br>Pin:<br>Pin:<br>Pin:<br>Pin: | : C1<br>: C2 | C4 |   |   |   |      |        |     |

# **NXP KINETIS PIN MAP for KW45 devices**

|       | ip Tool |       |       |       |                | 50.5 |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   |      |   |      |         |

|-------|---------|-------|-------|-------|----------------|------|----|----|----|----------|----|----|------|-------|------|-------|-------------|----------------|-------------------|-------------|--------|-------------------|-----|---|---|------|----------|---|------|---|------|---------|

| elect | your F  | lashk | Runne | er mo | del:           | FR 2 | 0  |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   | <br> |   | Expo | rt to I |

|       |         |       |       |       |                |      |    |    |    |          |    |    | Mast | ter b | oard | l con | nect        | or ((          | <b>.</b> 1        | - Ch.       | 8)     |                   |     |   |   |      |          |   |      |   |      |         |

| Ţ     |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   |      |   |      | L       |

| Γ     |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   |      |   |      | Ţ       |

|       |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   |      |   |      |         |

|       | 22      | 21    | 30    | 20    | <b>.</b><br>29 | 27   | 26 | 25 | 24 | <b>1</b> | 22 | 21 | 20   | 10    | 18   | 17    | 16          | 15             | 1/                | 12          | 12     | 11                | 10  | 9 | 8 |      | 6        | - | 2    |   | 1    |         |

|       |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   | <br> | _ |      |         |

| elect | a char  | inel: |       |       |                |      |    |    |    |          |    |    |      |       |      |       | Cor         | nnect          | ion d             | escrip      | otions | s:                |     |   |   |      |          |   |      |   |      |         |

|       | n.1 - k | W45   | Z410  | 53 [5 | WD             | j ,  |    |    |    |          |    |    |      |       |      |       |             | IO1:           |                   |             |        |                   |     |   |   | Pin: |          |   |      |   |      |         |

| e u   |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             | DIO2:          |                   |             |        |                   |     |   |   | Pin: |          |   |      |   |      |         |

| - CI  |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       | D           | NU3.           | UAR               | τ τχ        | (De    | vice              | RX) |   |   | Pin: | A2       |   |      |   |      |         |

|       |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       |             |                |                   |             |        |                   |     |   |   |      |          |   |      |   |      |         |

| e Ci  |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       | D           | 0IO4:          | UAR               | T RX        |        |                   |     |   |   | Pin: |          |   |      |   |      |         |

|       |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       | D<br>D      | 0IO4:<br>0IO5: | uar<br>Swe        | t rx<br>Dio | (De    | vice <sup>-</sup> |     |   |   | Pin: | C2       |   |      |   |      |         |

|       |         |       |       |       |                |      |    |    |    |          |    |    |      |       |      |       | D<br>D<br>D | 0IO4:<br>0IO5: | UAR<br>SWE<br>BOC | T RX        | (De    | vice <sup>-</sup> |     |   |   |      | C2<br>A3 |   |      |   |      |         |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

# **NXP KINETIS Memory Map**

# **NXP KINETIS Memory Map**

|   |              | MKE17Z256<br>KINETIS<br>NXP<br>KINETIS - lit | xxx7_1x_MX25L643 | 33F         |             |           |             |              |

|---|--------------|----------------------------------------------|------------------|-------------|-------------|-----------|-------------|--------------|

|   | Мето         | огу Туре                                     | Start Address *  | End Address | Memory Size | Page Size | Blank Value | Address Unit |

| 1 | [F] - Flash  |                                              | 0x0000000        | 0x0003FFFF  | 256.00 KiB  | 16        | 0xFFFFFFF   | BYTE         |

| 2 | [X] - Exterr | nal Memories                                 | 0x6000000        | 0x607FFFFF  | 8.00 MiB    | 256       | 0xFFFFFFF   | BYTE         |

|   |              |                                              |                  |             |             |           |             |              |

# **NXP KINETIS Memory Map for KW45 devices**

| )evici<br>iamily<br>1anu<br>Igori | r: KINETIS<br>facturer: NXP             |                 |             |             |           |             |              |

|-----------------------------------|-----------------------------------------|-----------------|-------------|-------------|-----------|-------------|--------------|

|                                   | Метогу Туре                             | Start Address * | End Address | Memory Size | Page Size | Blank Value | Address Unit |

| 1                                 | [f] - Program Flash                     | 0x0000000       | 0x0007FFFF  | 512.00 KiB  | 128       | 0xFFFFFFFF  | BYTE         |

| 2                                 | [r] - IFR0 - ROM Configure (OTP)        | 0x02000000      | 0x02001FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 3                                 | [u] - IFR0 - Customer Usage             | 0x02002000      | 0x02003FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 4                                 | [c] - IFR0 - CMAC Table                 | 0x02004000      | 0x02005FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 5                                 | [o] - IFR0 - Over-the-Air update        | 0x02006000      | 0x02007FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 6                                 | [F] - Secure Program Flash              | 0x1000000       | 0x1007FFFF  | 512.00 KiB  | 128       | 0xFFFFFFFF  | BYTE         |

| 7                                 | [R] - Secure IFR0 - ROM Configure (OTP) | 0x12000000      | 0x12001FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 8                                 | [U] - Secure IFR0 - Customer Usage      | 0x12002000      | 0x12003FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 9                                 | [C] - Secure IFR0 - CMAC Table          | 0x12004000      | 0x12005FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 10                                | [O] - Secure IFR0 - Over-the-Air update | 0x12006000      | 0x12007FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 11                                | [N] - Radio Narrowband Unit NBU         | 0x48800000      | 0x4883FFFF  | 256.00 KiB  | 1         | 0xFFFFFFFF  | BYTE         |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### → smh-tech.com

# SMH

# **NXP KINETIS Flash Configuration Field**

Flash Configuration Field is an area of Main Flash between the addresses **0x400** and **0x410**. In this area you can set some configuration for the device behaviour.

A random value written here may lock the device forever and any attempt to reprogram it will be failed.

After the execution of **#TPCMD** MASSERASE UNLOCK this area is blank with 0xFF value except for the **Flash Security Byte** that is 0xFE.

So, after **#TPCMD** MASSERASE UNLOCK command, the Flash memory is totally blank except for this 0xFE value and the Blankcheck operation will give you PASS.

Here an example of Flash Configuration Field for a Kinetis MKE1xZxx device:

| Flash Configuration Field Offset<br>Address | Size (Bytes) | Field Description                                                                                                               |

|---------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0x0_0400 - 0x0_0407                         | 8            | Backdoor Comparison Key. Refer to<br>Verify Backdoor Access Key command<br>and Unsecuring the MCU Using<br>Backdoor Key Access. |

| 0x0_0408 - 0x0_040B                         | 4            | Program flash protection bytes. Refer to<br>the description of the Program Flash<br>Protection Registers (FPROT0-3).            |

| 0x0_040F                                    | 1            | Data flash protection byte. Refer to the description of the Data Flash Protection Register (FDPROT).                            |

| 0x0_040E                                    | 1            | EEPROM protection byte. Refer to the<br>description of the EEPROM Protection<br>Register (FEPROT).                              |

| 0x0_040D                                    | 1            | Flash nonvolatile option byte. Refer to<br>the description of the Flash Option<br>Register (FOPT).                              |

| 0x0_040C                                    | 1            | Flash security byte. Refer to the<br>description of the Flash Security<br>Register (FSEC).                                      |

If the Kinetis device is not locked, so the **Flash Security Byte (FSEC)** that is set to **0xFE**, but the other protections bytes are not set to **0xFF**, the **#TPCMD** MASSERASE F command may fail.

# NXP KINETIS Flash Masserase Flash and Unlock

If you execute the **#TPCMD** MASSERASE F command after the **#TPCMD** CONNECT command, it may happen that **#TPCMD** MASSERASE F fails.

This is because Security Bytes could be set in the Flash (Security Bytes are other bytes than the Flash Security Byte).

It is therefore recommended to always execute the **#TPCMD** MASSERASE UNLOCK command before the **#TPCMD** MASSERASE F command.

What happens is that with the **#TPCMD** MASSERASE UNLOCK command all the Flash bytes are set to **0xFF** except the value of the **Flash Security Byte** which is set to **0xFE**.

Then if **#TPCMD** MASSERASE F command is then executed, the **Flash Security Byte** is also set to **0xFF**. So, at this point, all the Flash memory is in the erased state.

#### Please pay attention now.

If you perform a power off and power on of the board, the **Flash Security Byte** is set to **0xFF**, then the Flash will be secure and therefore to re-enter the device it will be necessary to re-set this byte back to **0xFE** (this is done automatically by the **#TPCMD** CONNECT command).

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

# **NXP KINETIS Flash Blankcheck**

When you run the #TPCMD BLANKCHECK F command you are trying to check if the Flash memory is in the erased state.

By implementation choice, the **#TPCMD** BLANKCHECK F command gives PASS both if the **Flash Security Byte FSEC** is equal to **0xFF** or if it is equal to **0xFE**.

All other bytes of Flash memory must be equal to 0xFF.

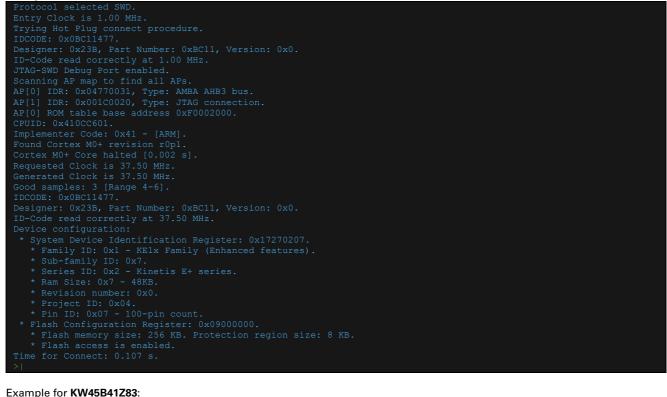

# **NXP KINETIS CPU Speed Calculation**

It is necessary for some specific Kinetis devices to calculate the working frequency of the core to correctly set a specific value in the Flash controller.

This is done empirically via a special procedure when executing the **#TPCMD** CONNECT command. Below you will find an example application case:

# ---fTPCMD CONNECT Protocol selected SWD. Entry Clock is 1.00 MHz. Trying Hot Plug connect procedure. IDCODE: 0x0BC11477. Designer: 0x23B, Part Number: 0xBC11, Version: 0x0. ID-Code read correctly at 1.00 MHz. JTAG-SWD Debug Port enabled. Scanning AP map to find all APs. AF(0) IDR: 0x001C0020, Type: AMBA AHB3 bus. AF(1) IDR: 0x001C0020, Type: JTAG connection. AP(0) ROM table base address 0xF0002000. CPUID: 0x410CC600. Implementer Code: 0x41 - [ARM]. Found Cortex M0+ revision r0p0. Cortex M0+ core halted [0.002 s]. Requested Clock is 37.50 MHz. Generated Clock is 37.50 MHz. Generated Clock is 37.50 MHz. Device configuration: \* System Reset Status and ID Register: 0x02140400. \* Family ID: 0x0 - KE0x family. \* Sub-family ID: 0x2. \* Revision number: 0x1. \* Pin ID: 0x4 - 32-pin. \* UID: 0x193D830630314534. Calculated frequency 15986 KHz, expected 16000 KHz [Δ -0.0875028]. Assuming bus frequency of ~16MHz [0x0F]. Time for Connect: 0.350 s.

# **NXP KINETIS FlexNVM Partitioning**

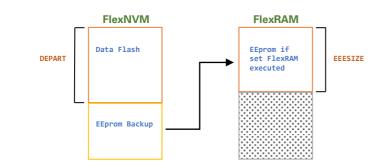

#### The basic idea is to divide the FlexNVM memory into two distinct areas.

The first area is always used for data use in which a single copy of the data is saved in each memory address (Data Flash). The second area into which the secondary flash is divided is called EEprom (EEprom Backup).

In reality it is always of flash technology being a part of Data Flash but the hardware behaviour of the EEprom is emulated. In fact, the Flash technology allows the rewriting of the memory cell of about 10'000 times while the EEprom technology allows the rewriting of 1'000'000 times of the data.

Therefore, to obtain this result in the secondary memory used (after the partitioning command) for EEprom use, a data is saved and copied several times of the EEprom backup memory.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

SMH

In this way an algorithm manages wear-levelling and it is possible to have the duration of a true EEprom. To divide the memory with the partitioning command it is necessary to specify specific parameters where the dimensions of the areas are indicated.

These parameters must be appropriately chosen so that the area reserved as data flash can contain all the data present in the source image file. The remaining free space can be used as a EEprom Backup.

# **Kinetis FlexRAM Partitioning Special Commands**

**#TPCMD** SET\_ FLEXRAM <RAM | EEPROM>

The Set FlexRAM command changes the function of the FlexRAM:

- When not partitioned for EEPROM, the FlexRAM is typically used as traditional RAM.

- When partitioned for EEPROM, the FlexRAM is typically used to store EEPROM data.

**#TPCMD** SET\_PARTITION <**FlexRAM** not loaded [1]/loaded [0]> <**EEPROM** Data Size> <**EEPROM**-backup Size> **#TPCMD** REMOVE\_PARTITION

To handle varying customer requirements, the FlexRAM and FlexNVM blocks can be split into partitions:

- EEPROM partition (EEESIZE) The amount of FlexRAM used for EEPROM can be set from 0 Bytes (no EEPROM) to the maximum FlexRAM size. The remainder of the FlexRAM not used for EEPROM is not accessible while the FlexRAM is configured for EEPROM. The EEPROM partition grows upward from the bottom of the FlexRAM address space.

- 2. Data flash partition (DEPART) The amount of FlexNVM memory used for data flash can be programmed from 0 bytes (all of the FlexNVM block is available for EEPROM backup) to the maximum size of the FlexNVM block.

- FlexNVM EEPROM partition The amount of FlexNVM memory used for EEPROM backup, which is equal to the FlexNVM block size minus the data flash memory partition size. The EEPROM backup size must be at least 16 times the EEPROM partition size in FlexRAM.

# Kinetis FlexNVM Partitioning Example

| 0x0000000<br>0x1000000                                                | 0x0007FFFF<br>0x1000FFFF                                                                          | 512.00 KiB<br>64.00 KiB                                                                                                                                          | 16<br>8                                                                                                                                      | 0xFFFFFFFF                                                                                                                                                                                      | BYTE<br>BYTE                                                                                                                                                                                    |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                       | 0x1000FFFF                                                                                        | 64.00 KiB                                                                                                                                                        |                                                                                                                                              | 0xFFFFFFFF                                                                                                                                                                                      | DIGTE                                                                                                                                                                                           |

| : loaded                                                              |                                                                                                   |                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                                 | BYIE                                                                                                                                                                                            |

| : Loaded                                                              |                                                                                                   |                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                 |

|                                                                       | [1]                                                                                               |                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                 |

| a Size                                                                | [512]                                                                                             |                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                 |

| up Size                                                               | [64]                                                                                              |                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                 |

| not loaded<br>Data Size se<br>Dackup Size<br>Dertition<br>Set partiti | during re<br>et to 512<br>set to 64<br>command.<br>on comman                                      | Bytes.<br>Kbytes.<br>nd.                                                                                                                                         |                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                 |

|                                                                       | ET_PARTITIO<br>on configur<br>not loaded<br>ata Size se<br>ackup Size<br>partition<br>Set partiti | ET PARTITION 1 512 6<br>on configuration:<br>not loaded during re<br>pata Size set to 512<br>cackup Size set to 64<br>partition command.<br>Set partition commar | ET_PARTITION 1 512 64<br>on configuration:<br>not loaded during reset sequer<br>Pata Size set to 512 Bytes.<br>Packup Size set to 64 Kbytes. | ET_PARTITION 1 512 64<br>on configuration:<br>not loaded during reset sequence.<br>Pata Size set to 512 Bytes.<br>Packup Size set to 64 Kbytes.<br>partition command.<br>Set partition command. | ET_PARTITION 1 512 64<br>on configuration:<br>not loaded during reset sequence.<br>Data Size set to 512 Bytes.<br>Dackup Size set to 64 Kbytes.<br>partition command.<br>Set partition command. |

UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

→smh-tech.com

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

SMH Technologies S.r.l.

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021

| SMH |  |

|-----|--|

|     |  |

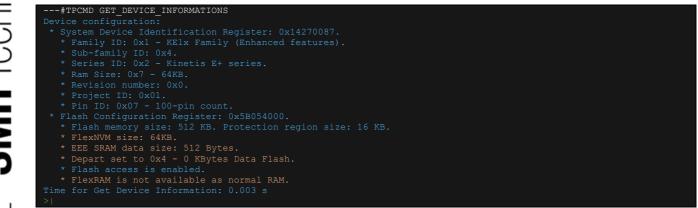

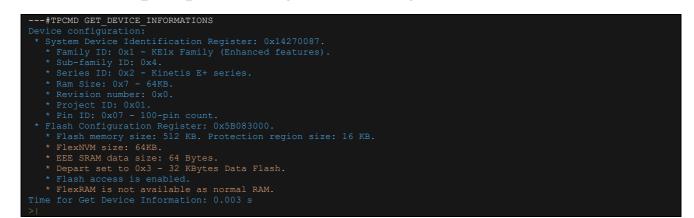

We use the **#TPCMD** GET DEVICE INFORMATIONS to get the new device configuration:

We use the **#TPCMD** SET\_PARTITION to change device partition:

FlexRAM loaded [0] EEPROM Data Size [64] EEPROM-backup Size [32] ---#TPCMD SET\_PARTITION 0 64 32 Set partition configuration: \* FlexRAM loaded with valid EEPROM data during reset sequence. \* EEPROM Data Size set to 64 Bytes. \* EEPROM-backup Size set to 32 Kbytes. FlexRVM is already divided into Data Flash and EEprom Backup. We need to remove partition before set the new one. To remove partition, we need to use Erase All Blocks command. This operation erases Flash memory, initialize FlexRAM, verifies all memory contents, releases MCU security. > Executed Remove partition command. Executed Set partition command. > Executed Set partition command. Time for Set Partition: 0.192 s >|

We use the **#TPCMD** GET DEVICE INFORMATIONS to get the new device configuration:

We use the **#TPCMD** REMOVE PARTITION to remove the partition already created:

---#TPCMD REMOVE\_PARTITION To remove partition, we need to use Erase All Blocks command. This operation erases Flash memory, initialize FlexRAM, verifies all memory contents, releases MCU security. > Executed Remove partition command. Time for Remove Partition: 0.162 s

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

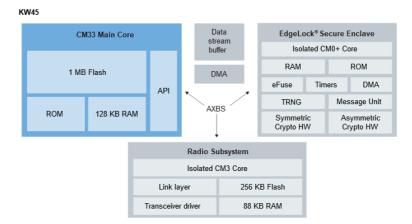

# **NXP KINETIS KW45 Devices**

Kinetis KW45's three-core architecture integrates a 96 MHz CM33 application core, dedicated CM3 radio core and an isolated EdgeLock Secure Enclave.

The Flash-based radio core with dedicated SRAM delivers a highly configurable and upgradeable software-implemented radio, freeing resources on the main core for customer application space.

The Bluetooth Low Energy 5.3-compliant radio supports up to 24 simultaneous secure connections. The EdgeLock Secure Enclave's isolated execution environment provides a set of cryptographic accelerators, key store operations and secure lifecycle management that minimizes main core security responsibilities.

The KW45 MCU additionally integrates FlexCAN, helping enable seamless integration into an automobile's in-vehicle or industrial CAN communication network.

The FlexCAN module can support CAN's flexible data rate (CAN FD) for increased bandwidth and lower latency.

# NXP KINETIS KW45 Architecture

# **NXP KINETIS KW45 Memory Map**

|    | Метогу Туре                             | Start Address * | End Address | Memory Size | Page Size | Blank Value | Address Unit |

|----|-----------------------------------------|-----------------|-------------|-------------|-----------|-------------|--------------|

| 1  | [f] - Program Flash                     | 0x00000000      | 0x0007FFFF  | 512.00 KiB  | 128       | 0xFFFFFFFF  | BYTE         |

| 2  | [r] - IFR0 - ROM Configure (OTP)        | 0x02000000      | 0x02001FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 3  | [u] - IFR0 - Customer Usage             | 0x02002000      | 0x02003FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 4  | [c] - IFR0 - CMAC Table                 | 0x02004000      | 0x02005FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 5  | [o] - IFR0 - Over-the-Air update        | 0x02006000      | 0x02007FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 6  | [F] - Secure Program Flash              | 0x1000000       | 0x1007FFFF  | 512.00 KiB  | 128       | 0xFFFFFFFF  | BYTE         |

| 7  | [R] - Secure IFR0 - ROM Configure (OTP) | 0x12000000      | 0x12001FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 8  | [U] - Secure IFR0 - Customer Usage      | 0x12002000      | 0x12003FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 9  | [C] - Secure IFR0 - CMAC Table          | 0x12004000      | 0x12005FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 10 | [O] - Secure IFR0 - Over-the-Air update | 0x12006000      | 0x12007FFF  | 8.00 KiB    | 128       | 0xFFFFFFFF  | BYTE         |

| 11 | [N] - Radio Narrowband Unit NBU         | 0x48800000      | 0x4883FFFF  | 256.00 KiB  | 1         | 0xFFFFFFFF  | BYTE         |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S\* 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

#### →smh-tech.com

# NXP KINETIS KW45 Available ISP commands

ISP commands availability is controlled by lifecycle and token. Table below shows the ISP commands available for each lifecycle. Details of several commands can be found in sections below.

| Command                                                                                                                                                                                                                                        | Description                                                                     | Before OEM<br>Open              | At OEM Open                     | After OEM<br>Open |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------|---------------------------------|-------------------|

| Reset                                                                                                                                                                                                                                          | Reset the device                                                                | Available                       | Available                       | Available         |

| get-property <tag></tag>                                                                                                                                                                                                                       | Query about various properties and settings                                     | Available                       | Available                       | Available         |

| set-property <tag> <value></value></tag>                                                                                                                                                                                                       | Change properties or options in ROM<br>Bootloader                               | Available                       | Available                       | Available         |

| receive-sb-file <file></file>                                                                                                                                                                                                                  | Receive a file in Secure Binary (SB) format                                     | Available                       | Available                       | Available         |

| flash-erase-region                                                                                                                                                                                                                             | Available                                                                       | With limitation for radio flash | NA                              |                   |

| flash-erase-all [ <memoryid>]</memoryid>                                                                                                                                                                                                       | Available                                                                       | With limitation for radio flash | NA                              |                   |

| read-memory <addr><br/><byte_count> [<file>]</file></byte_count></addr>                                                                                                                                                                        |                                                                                 |                                 | With limitation for radio flash | NA                |

| vrite-memory <addr> [<file>  <br/>{<hex-data>}}] Write memory at specified address from file or<br/>string of hex values<br/>Note: When write to SRAM, make sure the<br/>length of file or hex-data is 4-byte aligned</hex-data></file></addr> |                                                                                 | Available                       | With limitation for radio flash | NA                |

| fill-memory <addr><br/><byte_count> <pattern><br/>[word   short   byte]</pattern></byte_count></addr>                                                                                                                                          | Fill memory with pattern; pattern size can be word(default), short or byte      | Available                       | With limitation for radio flash | NA                |

| fuse-program <index> [<file><br/>  {{<hex-data>}}]</hex-data></file></index>                                                                                                                                                                   | Program fuse at the specified index from file<br>or string of hex values        | Available                       | Available                       | NA                |

| fuse-read <index><br/><byte_count> [<file>]</file></byte_count></index>                                                                                                                                                                        | Read fuse from the specified index                                              | Available                       | Available                       | NA                |

| Execute <address> <arg> <stackpointer></stackpointer></arg></address>                                                                                                                                                                          | Jumps to code at the provided address and does not return to the ROM bootloader | Available                       | Available                       | NA                |

# **NXP KINETIS KW45 Available Properties**

Table below shows the available properties (tag) for this device.

| Name                 | Writable | Tag value | Size in Bytes | Description                                    |

|----------------------|----------|-----------|---------------|------------------------------------------------|

| CurrentVersion       | no       | 1         | 4             | The current bootloader version.                |

| AvailablePeripherals | no       | 2         | 4             | The set of peripherals supported on this chip. |

| FlashStartAddress    | no       | 3         | 4             | Start address of program flash.                |

| FlashSizeInBytes     | no       | 4         | 4             | Program flash size in bytes.                   |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

| FlashSectorSize    | no  | 5  | 4  | The size of one sector of program flash in bytes.                                                                                                                                                                                                                                                               |

|--------------------|-----|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FlashBlockCount    | no  | 6  | 4  | The number of blocks of the on-chip flash.                                                                                                                                                                                                                                                                      |

| AvailableCommands  | no  | 7  | 4  | The set of commands supported by the bootloader.                                                                                                                                                                                                                                                                |

| CRCCheckStatus     | no  | 8  | 4  | The status of the application CRC check.                                                                                                                                                                                                                                                                        |

| VerifyErase        | yes | 10 | 4  | Controls whether the bootloader verifies eras<br>to flash. The VerifyErase feature is enabled<br>by default:<br>1 = Enable<br>0 = Disable                                                                                                                                                                       |

| MaxPacketSize      | no  | 11 | 4  | Maximum supported packet size for the currently active peripheral interface.                                                                                                                                                                                                                                    |

| ReservedRegions    | no  | 12 | 4  | List of memory regions reserved<br>by the bootloader. Returned as<br>value pairs ( <startaddress-ofregion>, <end-<br>addressof-region&gt;).</end-<br></startaddress-ofregion>                                                                                                                                   |

| RAMStartAddress    | no  | 14 | 4  | Start address of RAM                                                                                                                                                                                                                                                                                            |

| RAMSizeInBytes     | no  | 15 | 4  | RAM size in bytes.                                                                                                                                                                                                                                                                                              |

| SystemDeviceId     | no  | 16 | 4  | System Device ID                                                                                                                                                                                                                                                                                                |

| SecurityState      | no  | 17 | 4  | Security status                                                                                                                                                                                                                                                                                                 |

| UniqueDeviceId     | no  | 18 | 16 | Unique device identification                                                                                                                                                                                                                                                                                    |

| BootStatus         | no  | 20 | 4  | Value of Boot Status Register                                                                                                                                                                                                                                                                                   |

| LoadableFWVersion  | no  | 21 | 4  | SSS loadable firmware version                                                                                                                                                                                                                                                                                   |

| FuseProgramVoltage | yes | 22 | 4  | Control the System LDO VDD Regulator<br>Voltage Level. To program fuse, System LDO<br>VDD regulator level needs to be regulated to<br>Over Drive Voltage (2.5 V). The default System<br>LDD VDO Regulator Voltage Level is regulate<br>to Normal Voltage (1.8 V).<br>0 = System LDO VDO Regulator Voltage Level |

|                    |     |    |    | is related to Normal Voltage (1.8 V)<br>1 = System LDO VDD regulator level is<br>regulated to Over Drive Voltage (2.5 V)                                                                                                                                                                                        |

| TargetVersion      | no  | 24 | 4  | Target version                                                                                                                                                                                                                                                                                                  |

SMH Technologies S.r.l.

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale

Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 **D-U-N-S**<sup>®</sup> 51-724-9350 **T** + 39 0434 421 111 **F** + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

info@smh-tech.com

SMH

# NXP KINETIS KW45 Available eFUSE

| Name                                     | Fuse index | Description                                                                                                                                                              |

|------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIFECYCLE                                | 0x0A       | Lifecycle state.                                                                                                                                                         |

|                                          |            | Corresponding product state can be determined from Table 1.<br>Lifecycle States                                                                                          |

| DBG_EN_LOCK                              | 0x0B       | Debug Enable Lock                                                                                                                                                        |

|                                          |            | 0b - The debug access control registers remain open when jumping to customer code.                                                                                       |

|                                          |            | 1b - The debug access control registers are write-locked before jumping to customer code.                                                                                |

| DBG_AUTH_DIS                             | 0x0C       | Debug Authentication Disabled                                                                                                                                            |

|                                          |            | 0b - Debug Authentication enabled.                                                                                                                                       |

|                                          |            | 1b - Debug Authentication disabled.                                                                                                                                      |

| TZM_EN                                   | 0x0D       | Trust Zone Mode Enable                                                                                                                                                   |

|                                          |            | 0b - TZ-M is disabled by default.                                                                                                                                        |

|                                          |            | 1b - TZ-M is enabled.                                                                                                                                                    |

| SERIAL_DIS                               | 0x11       | Serial Download Disabled                                                                                                                                                 |

|                                          |            | 0b - ISP path is enabled.                                                                                                                                                |

|                                          |            | 1b - ISP path is disabled.                                                                                                                                               |

| WAKEUP_DIS                               | 0x12       | Wakeup Disabled                                                                                                                                                          |

|                                          |            | 0b - Boot-ROM LP wakeup is enabled.                                                                                                                                      |

|                                          |            | 1b - Boot-ROM LP wakeup is disabled.                                                                                                                                     |

| CUST_PROD_OEMFW_AUTH_P<br>UK_REVOKE[3:0] | 0x13       | Key revocation indicators of CUST_PROD_OEMFW_AUTH_PUK.                                                                                                                   |

| DBG_AUTH_VU[15:0]                        | 0x15       | These Debug Authentication Vendor Usage fuses are used by customers to restrict debug certificates.                                                                      |

| IMG_KEY_REVOKE[15:0]                     | 0x16       | These fuses are used to revoke image signing keys separately from root keys.                                                                                             |

| SECURE_PHANTOM_CONFIG                    | 0x18       | Token configuration.                                                                                                                                                     |

| CUST_PROD_OEMFW_AUTH_P<br>UK             | 0x1f       | 256-bit RoTKTH (customer trusted root key) typically used for CM33 main flash image authentication.                                                                      |

| CUST_PROD_OEMFW_ENC_SK                   | 0x20       | 256-bit encryption key used to protect confidentiality of OEM firmware.<br>Typically required for firmware updates using sb3 (SB3KDK).                                   |

| OEM_Enablement_Token                     | 0x21       | 256-bit RoTKTH (root key hash) typically used for radio firmware<br>authentication. (if valid token is intended to be used by programming<br>SECURE_PHANTOM_CONFIG fuse) |

| DCFG_CC_SOCU_L1[8:0]                     | 0x22       | Debug authentication configuration for level 1 customer.                                                                                                                 |

| DCFG_CC_SOCU_L2[8:0]                     | 0x23       | Debug authentication configuration for level 2 customer.                                                                                                                 |

HQ and Registered Office Via Giovanni Agnelli 1 33083 Villotta di Chions (PN) Italy Società Unipersonale Capitale sociale €102.040 P.I. 01697470936 C.F. 01697470936 REA PN-97255 D-U-N-S<sup>®</sup> 51-724-9350 T + 39 0434 421 111 F + 39 0434 639 021 UNIVERSAL PRODUCTION IN-SYSTEM PROGRAMMING

info@smh-tech.com

| SOC_VER_CNT                         | 0x24 | 512-bits of version counter for various software components in SoC.<br>Each software component version counter has dedicated fuse index<br>0x25 to 0x29. |

|-------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM33_S_VER_CNT                      | 0x25 | 64-bit secure OEM CM33 firmware version counter (number of set fuse bits).                                                                               |

| CM33_NS_VER_CNT                     | 0x26 | 256-bit non-secure OEM CM33 firmware version counter (number of set fuse bits).                                                                          |

| RADIO_VER_CNT                       | 0x27 | 128-bit radio firmware version counter (number of set fuse bits).                                                                                        |

| SNT_VER_CNT                         | 0x28 | 32-bit s200 loadable firmware version counter (number of set fuse bits).                                                                                 |

| CM33_BOOTLOADER_VER_CNT             | 0x29 | Reserved for future usage of additional NXP software deliverable.                                                                                        |

| CM33_S_VER_CNT_VIRTUAL              | 0x2A | 64-bit secure OEM CM33 firmware version counter (Integer value equivalent to number of set fuse bits).                                                   |

| CM33_NS_VER_CNT_VIRTUAL             | 0x2B | 256-bit non-secure OEM CM33 firmware version counter (Integer value equivalent to number of set fuse bits).                                              |

| RADIO_VER_CNT_VIRTUAL               | 0x2C | 128-bit radio firmware version counter (Integer value equivalent to number of set fuse bits).                                                            |

| SNT_VER_CNT_VIRTUAL                 | 0x2D | 32-bit s200 loadable firmware version counter (Integer value equivalent to number of set fuse bits).                                                     |

| CM33_BOOTLOADER_VER_CNT<br>_VIRTUAL | 0x2E | Reserved for future usage of additional NXP software deliverable.                                                                                        |

# **NXP KINETIS KW45 Specific Commands**

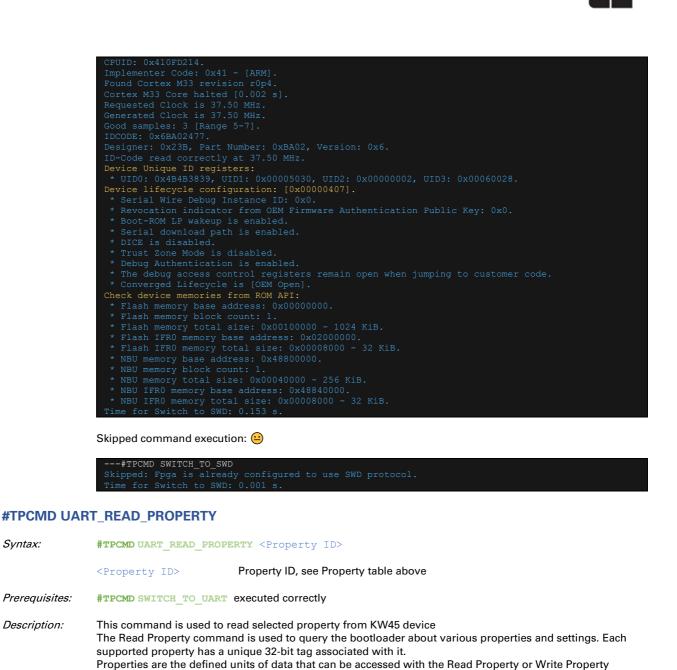

One of the most important features of the Kinetis KW45 device is that it is not possible to perform all operations using only the **SWD** protocol.

In fact, it is also necessary to use the **UART** protocol.

Through FlashRunner you can use the **UART** and **SWD** simultaneously in the same channel.

Special commands have therefore been added for the KW45 device.

Commands for switch from SWD to UART and vice versa:

**#TPCMD** SWITCH\_TO\_SWD **#TPCMD** SWITCH\_TO\_UART

UART commands for read and write properties:

**#TPCMD** UART\_READ\_PROPERTY **<Property ID> #TPCMD** UART WRITE PROPERTY **<Property ID> <Property Value>**

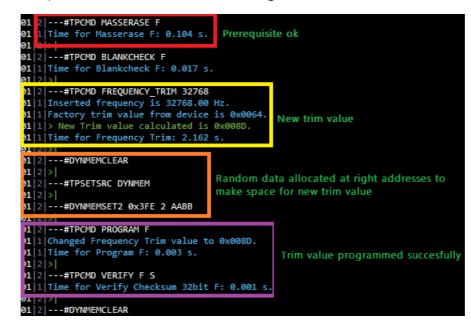

#### UART commands for erase memory regions:

**#TPCMD** UART\_FLASH\_ERASE\_ALL <INTERNAL\_FLASH|RADIO\_PFLASH|RADIO\_USER\_IFR> **#TPCMD** UART FLASH ERASE REGION <Address> <Byte Count> <INTERNAL FLASH|RADIO PFLASH|RADIO USER IFR>

#### UART commands for read memory regions: